主题中讨论的其他器件: CSD19531Q5A

你(们)好。

我们的电路板设计用于5.2V 6A 和7.4V 18A 输出、运行电压为30-48V。 我们在运行和上电期间看到一些故障。 还有一些电路板工作正常、温度不超过预期值。

在一种情况下、LM5116芯片烧毁、而在另一种情况下、电压低于预期值、另一个芯片发热。 一些电路板工作正常。 7.4V 布局和5.2V 布局非常相似、并基于 EVAL 板中的指南: www.ti.com/.../snva285a.pdf

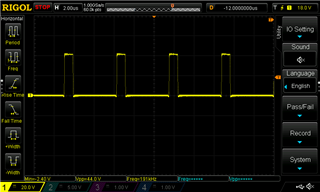

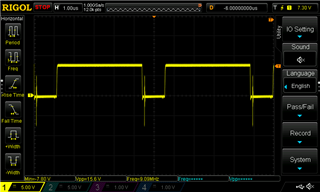

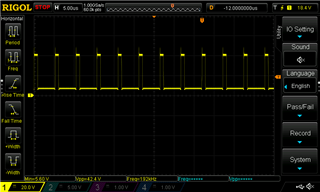

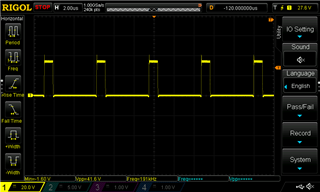

我在测量 MOSFET 上的 HO 和 LO 时看到的是、LO 在高电流时具有非常负的尖峰、我想知道这是否是故障的原因? 根据我所读到的文章,这里似乎出现了一些消极的瞬变。 是否仍然需要验证这是导致 LM5116故障的原因、例如以某种方式测量故障芯片?

我还注意到我们的 CSD19531Q5A MOSFET 226nC QRR 相对较高、这是否会导致负尖峰?

HO、LO、SW (引脚20)、HB (引脚18)

根据 Excel 设计、我认为组件选择和布局应该可以、我也附上了这些组件 以供参考。

e2e.ti.com/.../0284.PCB.pdfe2e.ti.com/.../8345.Schematic.pdf