您好!

我对如何使 UCC27OH 的输出作为数据表发挥作用有一些疑问。

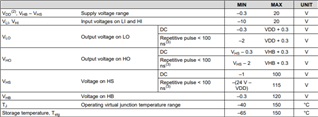

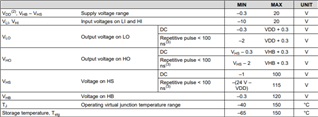

根据第5页的信息、输出 VLO 和 VHO 的最大值为 VDD+0.3和 VHB+0.3。

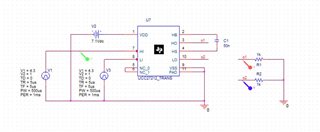

这里是我在 PSpice 中的电路和仿真结果、一切看起来都很好。 VLO 和 VHO 都几乎达到 VDD (7V)。

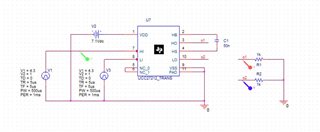

但是、当我使用同一电路进行实际测试时、我得到了一个偏心波形。 下一幅图像是 VLO、它显然小于预期值。 VHO 几乎与 VHS 相同、因此高侧的输出接近于零。 这个波形很难驱动 MOS。

谢谢

Auold

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我对如何使 UCC27OH 的输出作为数据表发挥作用有一些疑问。

根据第5页的信息、输出 VLO 和 VHO 的最大值为 VDD+0.3和 VHB+0.3。

这里是我在 PSpice 中的电路和仿真结果、一切看起来都很好。 VLO 和 VHO 都几乎达到 VDD (7V)。

但是、当我使用同一电路进行实际测试时、我得到了一个偏心波形。 下一幅图像是 VLO、它显然小于预期值。 VHO 几乎与 VHS 相同、因此高侧的输出接近于零。 这个波形很难驱动 MOS。

谢谢

Auold

您好、Auold、

为了使 HO 输出运行、HB-HS 偏置需要通过内部自举二极管从 VDD 充电。 这通常发生在典型的 MOSFET 半桥配置中、驱动器的 HS 引脚连接到 MOSFET 高侧源极和低侧漏极公共连接。 当低侧 MOSFET 导通时、HS 引脚 开关接近 接地、HB-HS 电容器通过自举二极管从 VDD 充电。

在您测试的应用中、HS 引脚是通过 外部 MOSFET 半桥切换到接地还是通过其他路径从 HS 接地? 仿真原理图未显示 HS 与外部功率晶体管的连接。 此外、LO 需要切换 以允许对自举偏置进行充电。

确认这是否能解决您的问题、或者您可以在此主题上发布其他问题。

此致、

您好、Auold、

感谢您确认对 HS 引脚上某些连接/路径的需求的理解。

如果驱动器输出全部悬空、HB 电容器将不会像您提到的那样充电。

有关 LO 开关的注释。 在某些情况下、即使连接了功率 MOSFET、如果不驱动两个 MOSFET、HS 引脚接地端仍可能存在高电阻。 当 LO 打开时、HS 接地开关可确保 HB 电容器有一条充电路径从 VDD 充电。 根据连接到开关节点的动力总成元件、HB 电容器可能有充电路径、但在某些情况下可能没有充电路径。

安全的测试方法是连接功率 MOSFET、但不向 MOSFET 半桥施加高压。 低侧 FET 开关仍会为 HB 电容器充电、您可以检查驱动器输出。

确认这是否能解决您的问题、或者您可以在此主题上发布其他问题。

此致、

您好 Richard、

您应该解释一下该机制并告诉我如何安全地进行测试。 请原谅我的无知、我仍然对 VLO 的输出波形有问题。

在我的仿真结果(图3)中、VLO 的高电平(蓝色)约为7V、这几乎跟随 VDD、而 VLO 的低电平约为0V。 但在我的实验(图4)中、当 VDD 也为7V 时、VLO 的高电平为4.635V、而 VLO 的低电平为1.435V、这与仿真完全不同。 这种情况是否归因于驱动器输出的开路? 为什么波形的高电平如此低、而低电平如此高?

谢谢。

您好、Auold、

感谢您再次提到对 LO 级别的关注。 如果 LO 输出仅为 MOSFET 的栅极 Qg 充电、并且驱动器接地和低侧 MOSFET 接地相同、则 LO 应从接近0和 VDD 过渡、如仿真所示。 似乎必须有负载 LO 驱动器输出或接地漂移或两者的东西。

您能否共享实际测试的硬件原理图以供审阅? 我可以回顾一下是否有明显的情况。 此外、检查驱动器、驱动器与 MOSFET 等的电路板连接 使用 DVM 检查 MOSFET 栅极至源极、并查看是否存在一些低电阻。 确认低侧的 MOSFET 源极引脚已接地。

如果您不想将原理图发布在该主题上、您可以与我建立好友关系、并能够进行私密通信。

此致、