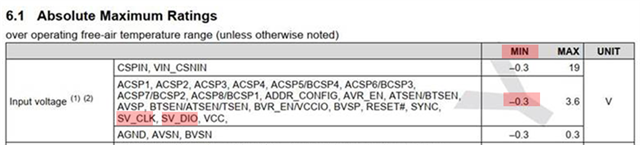

0.3V 电压联合定义的 SCL 和 SDA 绝对额定值是什么? 是直流电压还是峰值电压?

情况如下。

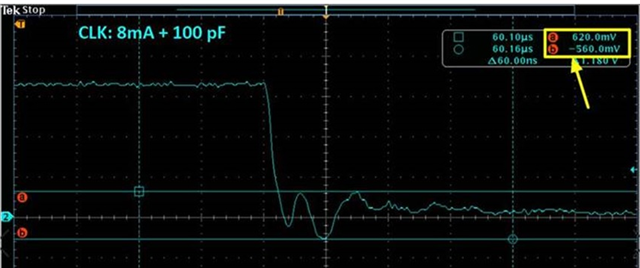

当 SCL 信号峰值为-0.56V 时会出现负振铃 、但数据表显示了绝对最小值。负电压规格为-0.3V。

请注意:信号低电平周期电压电平为32mV

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Jacky、

首先、我建议确保测量值为真实值、但在 IC 引脚处使用差分探头进行检查。 波形看起来可能比 IC 实际看到的波形更差。

略微超过器件的绝对最大规格不会导致灾难性故障、但可能会导致 IC 中器件随着时间的推移而加速老化和移位。 我们不能保证这一长期存在。 我认为这"可能"是可以的、因为超过绝对最大额定值的持续时间仅为几 ns、超过最大额定值的寿命平均占空比将极小。 但是、正如我之前所说的、通过加入一个与 SCL 线路串联的电阻器、您也许仍然能够在不降低性能的情况下改进波形。

您好、Matt、

感谢您的反馈、我 将关键概念总结如下:

"略微超过器件的绝对最大规格不会导致灾难性故障、但可能会导致 IC 中器件随着时间的推移而加速老化和移位。"

" TI 提到、通过添加一个与 SCL 线路串联的电阻器、可以改善-0、56V 的干扰噪声。"

BTW、我的最后两个问题如下:

Q1:"为什么器件的 SCL 和 SDA 的负最小规格 不符合 SMBus 标准? "

所有 MB 与 SMBus 相关的器件的规范都是负最小值。确实遵循了 SMBus 标准、最小值为 -0.5V。

例如 BMC 和 CPLD IC。

Q2:IC 的 ESD 电路 VS 毛刺脉冲噪声-0.56V VS 绝对额定最小电压单位 -0.3VDC

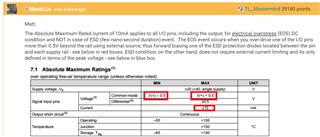

基于以下网站、显示该单元是 绝对额定最小直流电压

https://e2e.ti.com/support/amplifiers/f/amplifiers-forum/572781/opa172-output-protection

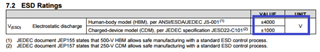

根据上述说明、如果 IC 确实通过了 JEDEC JEP-22-C101相关 ESD 标准。

该器件的内部 EDS 保护 TVS 二极管将作用并保护 IC。

我确实理解添加一个串联电阻可以限制毛刺脉冲噪声的电流、并防止因 EOS 电流而不是 EOS 电压而损坏 IC 的内部 TVS 二极管。

正因为当干扰负电压发生时、TVS 二极管将作为正向条件打开。

在这种情况下、当 TVS 二极管上出现毛刺脉冲负电压时、电流和能量都相关。

您能 帮助确认我的理解是否正确吗?

您好、Matt、

我的老板有以下问题:

PMBus ESD 单元二极管额定正向电压和电流 VS PMBus 绝对最大值 额定电压(-0.3V 最小值)

ESD 单元二极管的额定正向电压和电流是多少?

在 TPS53688数据表下方、数据表显示 IOL =-20mA

![]()

这20mA 直流电流是否也等于 ESD 单元二极管的额定正向电流?

这个0.3V 是否也等于 ESD 单元的二极管额定正向电压?

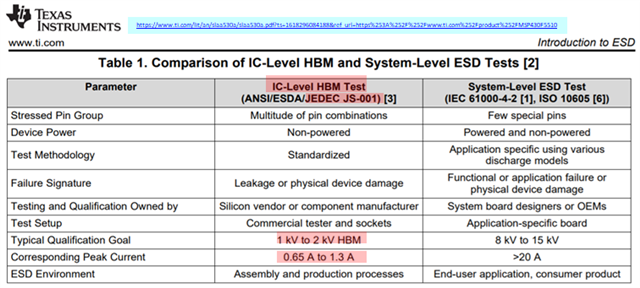

2. HBM ESD 测试 (JES-001) 与 IC 的所有 I/O 引脚的关系

所有 I/O 引脚是否都通过了 HBM ESD 测试并且能够处理0.65A 峰值电流至1.3A 峰值电流?

此致

张学友

您好、Jacky、

1-这些规格与 ESD 二极管无关、它们为 PMBus 数据驱动器的强度(下拉电阻)提供了测试限制。 这基本上是说、当打开时(例如发送数据"0")、TPS53688数据 IO 拉低、最大值为0.4V/0.02A = 20欧姆。 该值为负、因为器件在此期间通过上拉电阻器灌入电流。

2:所有 IO 引脚都已通过此器件的2kV HBM ESD 认证。 HBM ESD 测试主要涉及将电容器充电至2kV、并通过电阻器将其放电到器件中。 峰值电流约为1.3A、但在非常短的时间内、仅为几十纳秒。