主题中讨论的其他器件:TPS51916、

尊敬的技术支持团队:

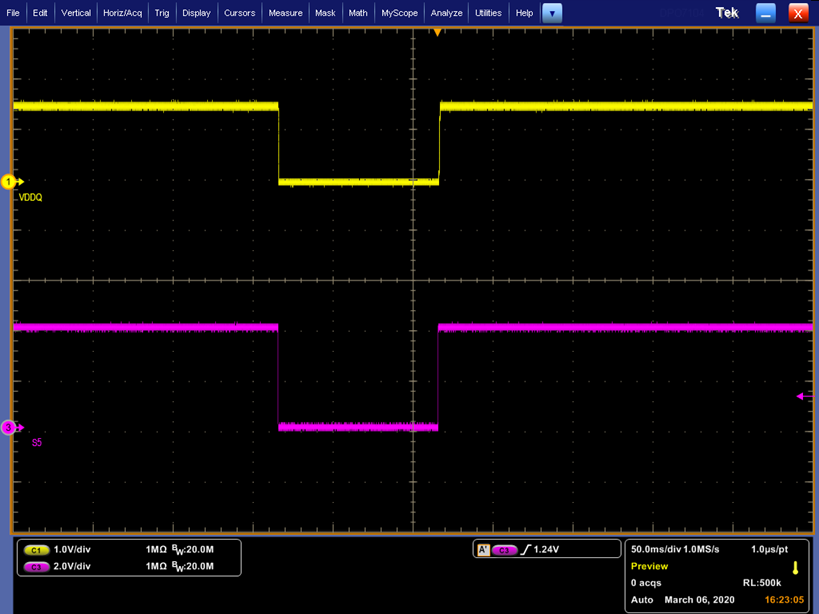

——您能给我最小的 S5信号无效时间吗?

-您能否告诉我在[波形(A)]的情况下 VDDQ 为什么没有上升?

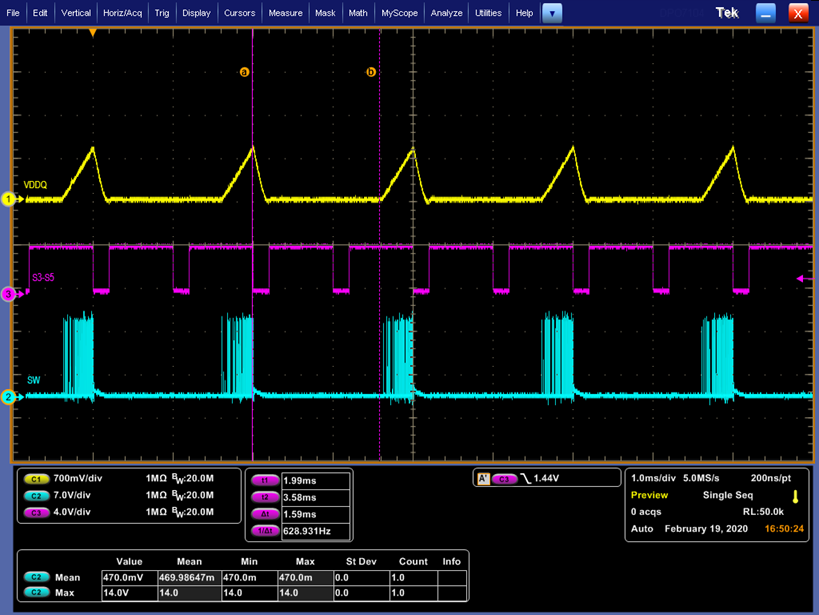

[波形(A)]

我注意到,在200us 的断言之后,VDDQ 没有上升

信号的频率。

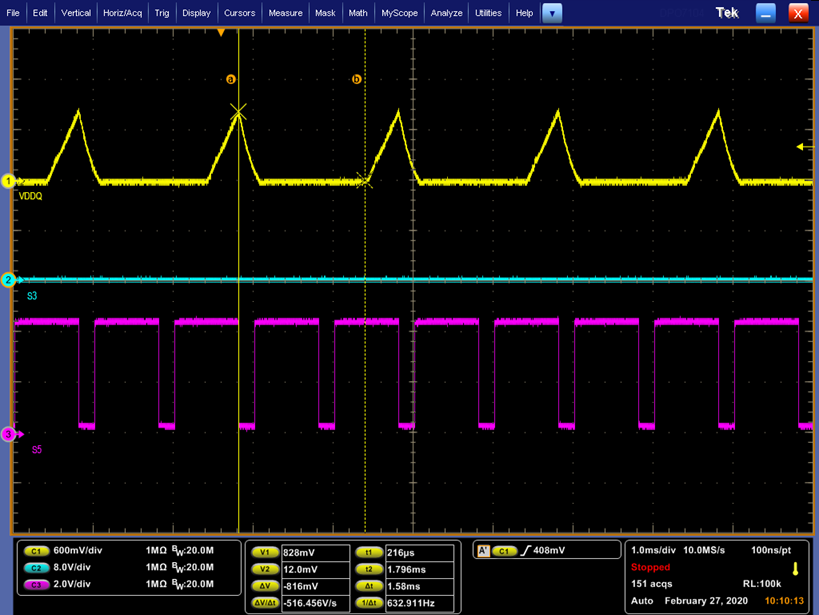

[波形(B)]

但在 S5信号无效4、000ms 后、VDDQ 确实上升。

我已查看波形(A)和(B)。 不同之处在于断言

信号的时间。 因此、我们认为最短时间是最短的

使 S5信号无效以重新上升 VDDQ。

此致、

Hirose 总一郎

e2e.ti.com/.../Question_5F00_min_2D00_low_2D00_time_2D00_about_2D00_S5.pdf