技术人员或经理、您好!

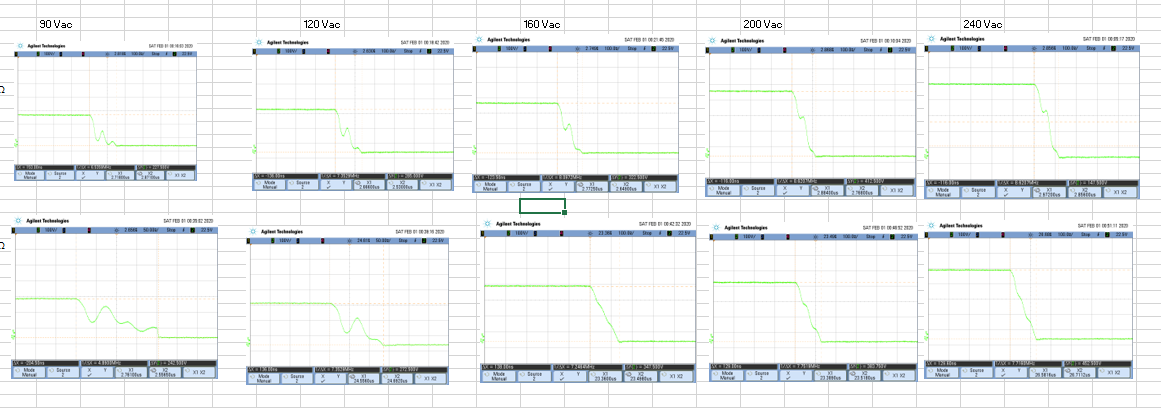

我使用 UCC28780设计了65W 原型。 我发现、在90Vac 输入下、 当负载电流从0A 增加到3.25A 时、Vout 仅下降0.07V。

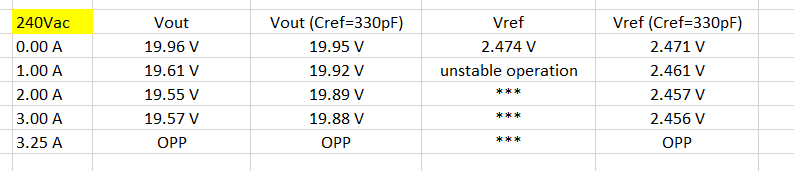

但是、当线路输入电压增加到220Vac 或240Vac 时、Vout 从0A 下降到满载(3.25A)的电压接近0.9V。

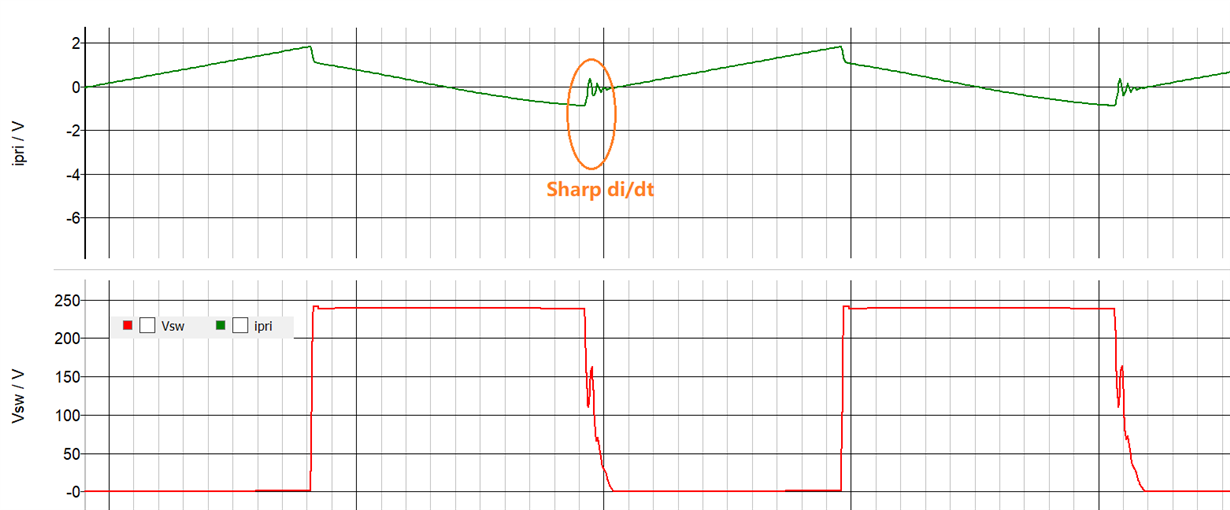

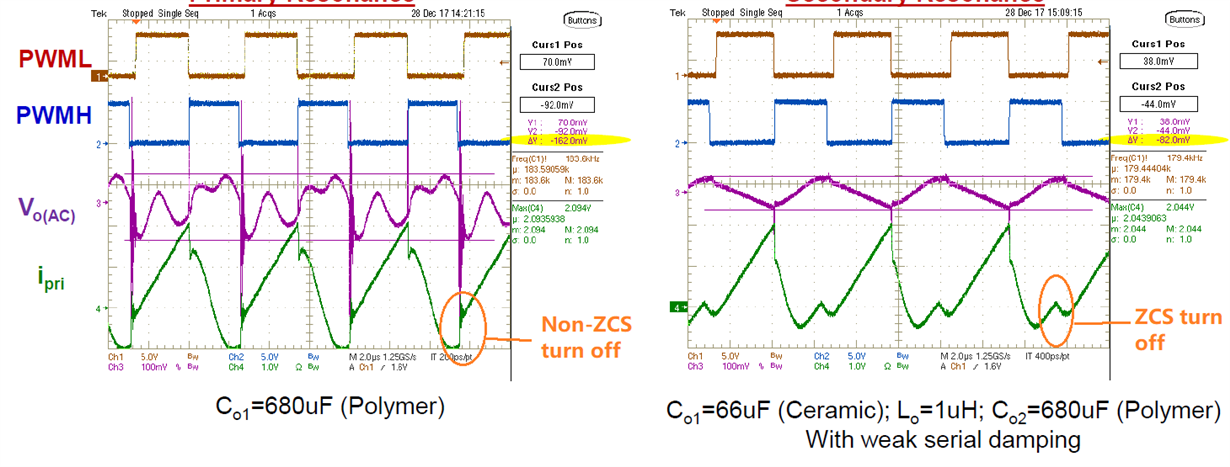

我尝试将 Ropp 从1kOhm 降低到250 Ohm、但它不起作用。 我尝试将 Cout 从680uF 增加到1360uF、并且在高线路输入端 Vout 也从0A 大幅下降到3.25A。

什么可能导致此类问题? 您能给我一些关于如何解决的建议吗? 谢谢!