主题中讨论的其他器件: CSD87381P、 BOOSTXL-TPS650861、 CSD87331Q3D、 IPG-UI、 USB2ANY

尊敬的专家:

几个月前、在您的帮助下、我们通过 此主题 https://e2e.ti.com/support/power-management/f/196/t/875459找到了 TPS650864评估板的焊接问题。 重新焊接电路板后、我们得到了新电路板。

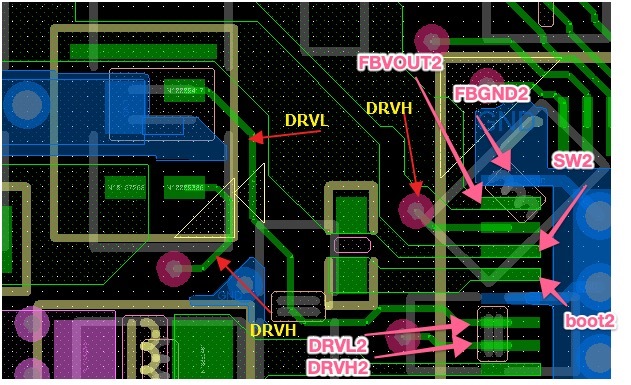

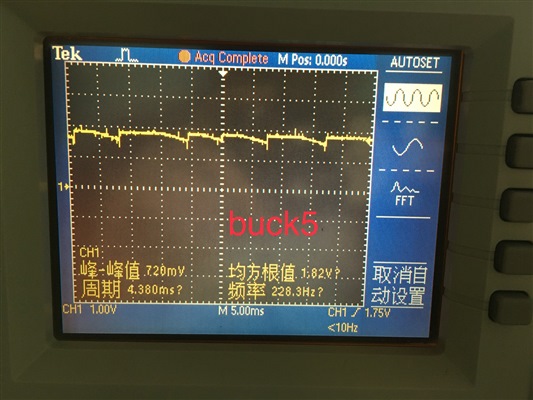

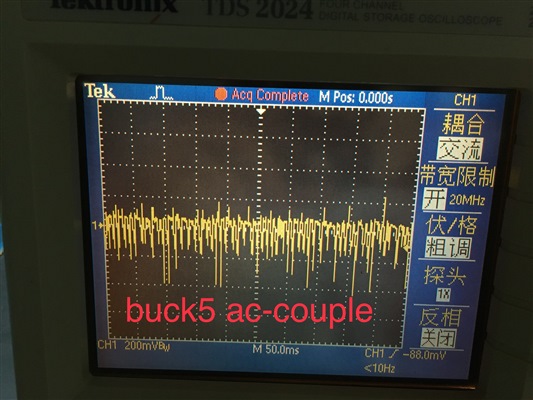

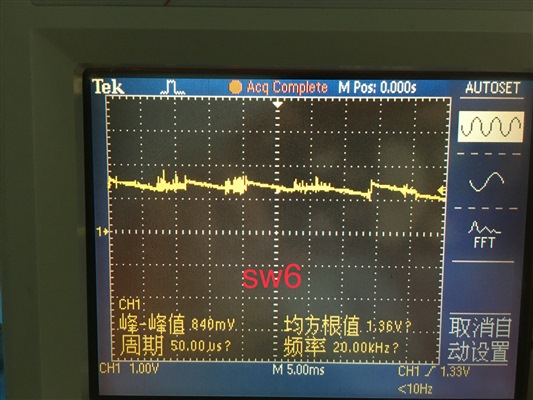

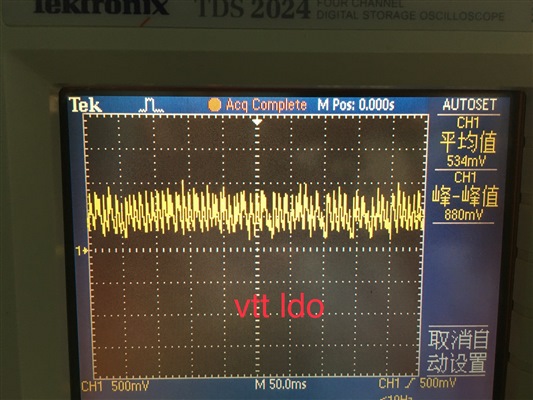

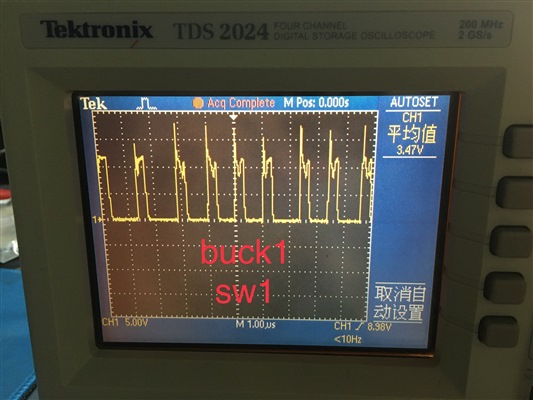

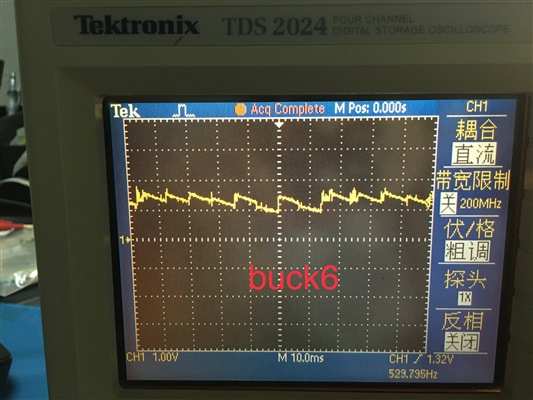

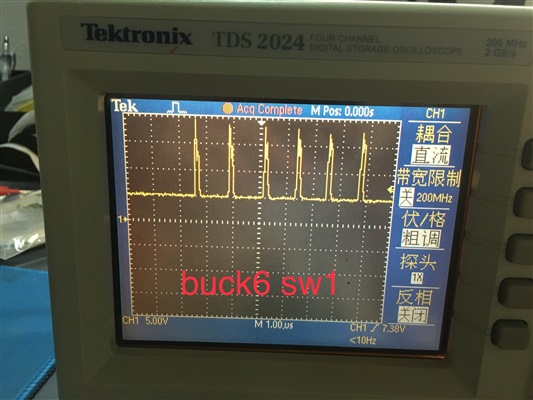

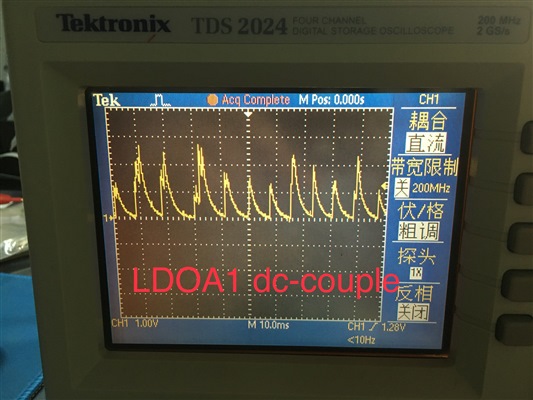

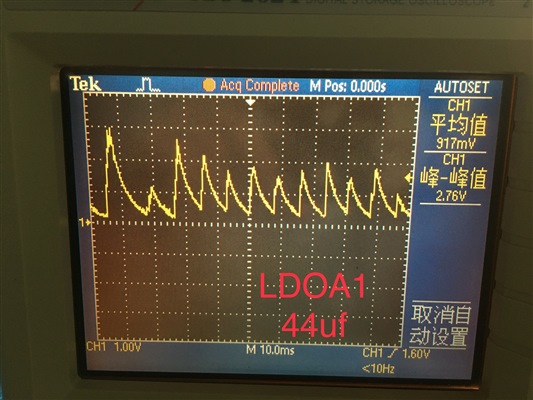

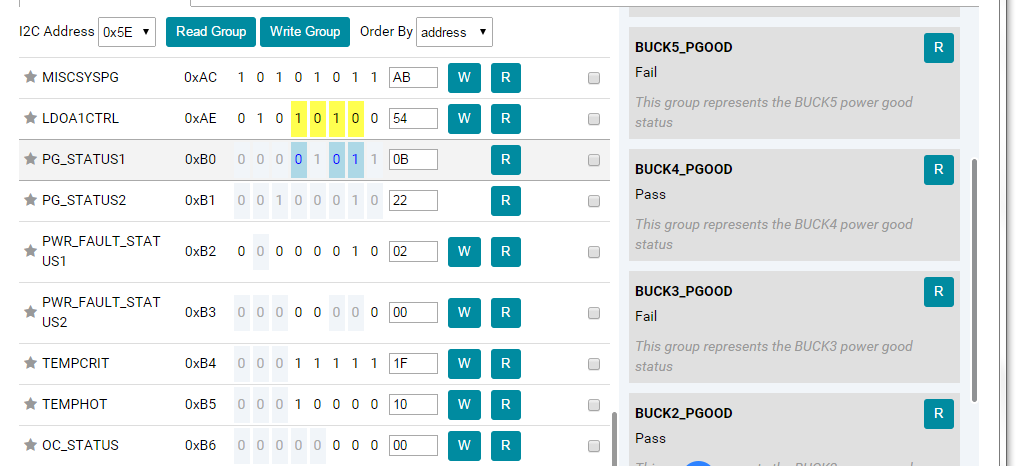

在测试中、LDO5V5和 LDO3V3都正确。 在探测 SW2输出时、预期提供0.85V 电压、它似乎无法正常工作。 输出电压不稳定、从0.5V 跳至4V、来回跳变、总电流在0.1A 至0.4A 范围内变化、输入电压为12V。 芯片有点热。 由于 SW2处于非正常状态、其他电源轨没有输出。

我的问题如下:

什么因素可能导致 SW2不正常状态? 作为 TPS650864芯片的新手、欢迎您提出任何建议。

2.如果我们要切断 SW2并让其他电源轨工作、如何实现? 为了使 SW1正常工作、我们尝试了仅在 CTL4上拉高电平、但它不起作用。

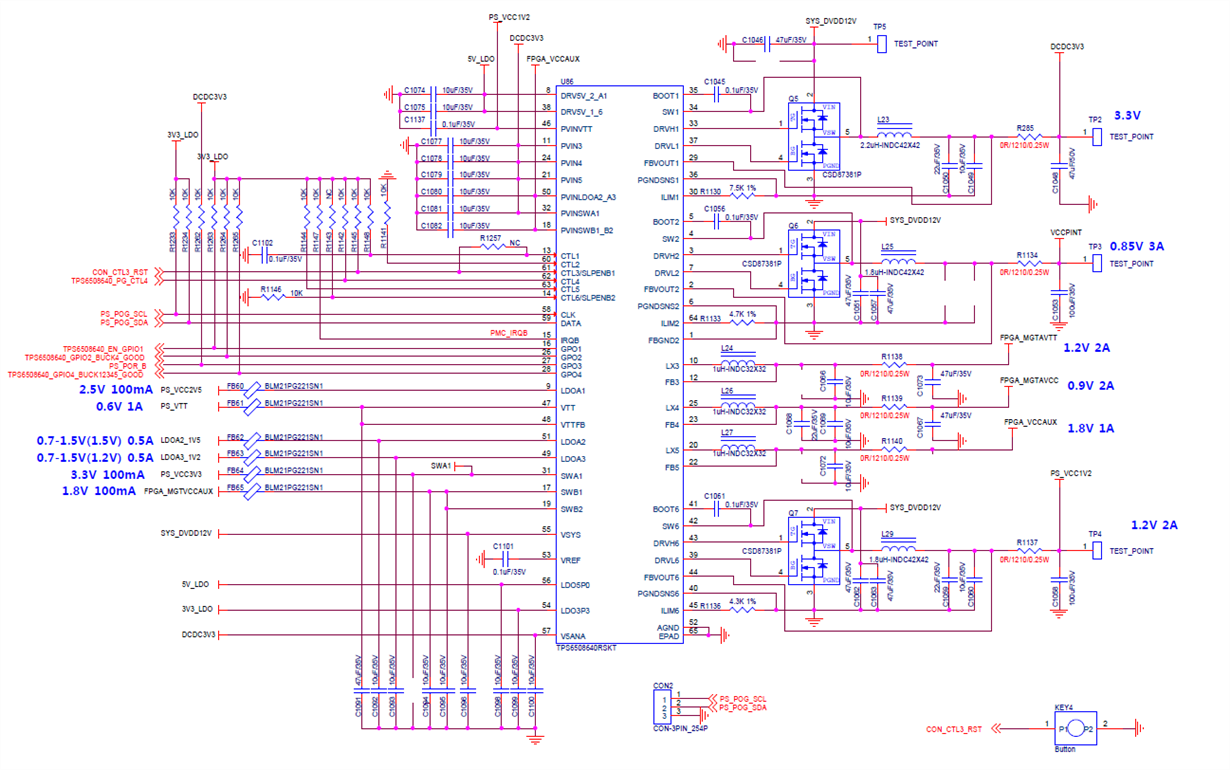

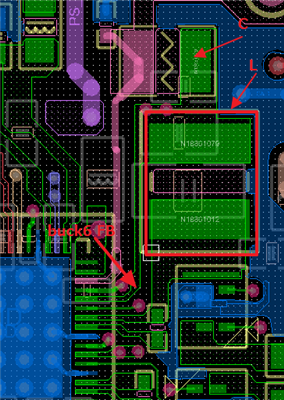

3.在以下原理图中,您能帮助检查 SW2的电路吗?

谢谢您的观看