主题中讨论的其他器件: PMP10555、 PMP20080、 TPS544C20

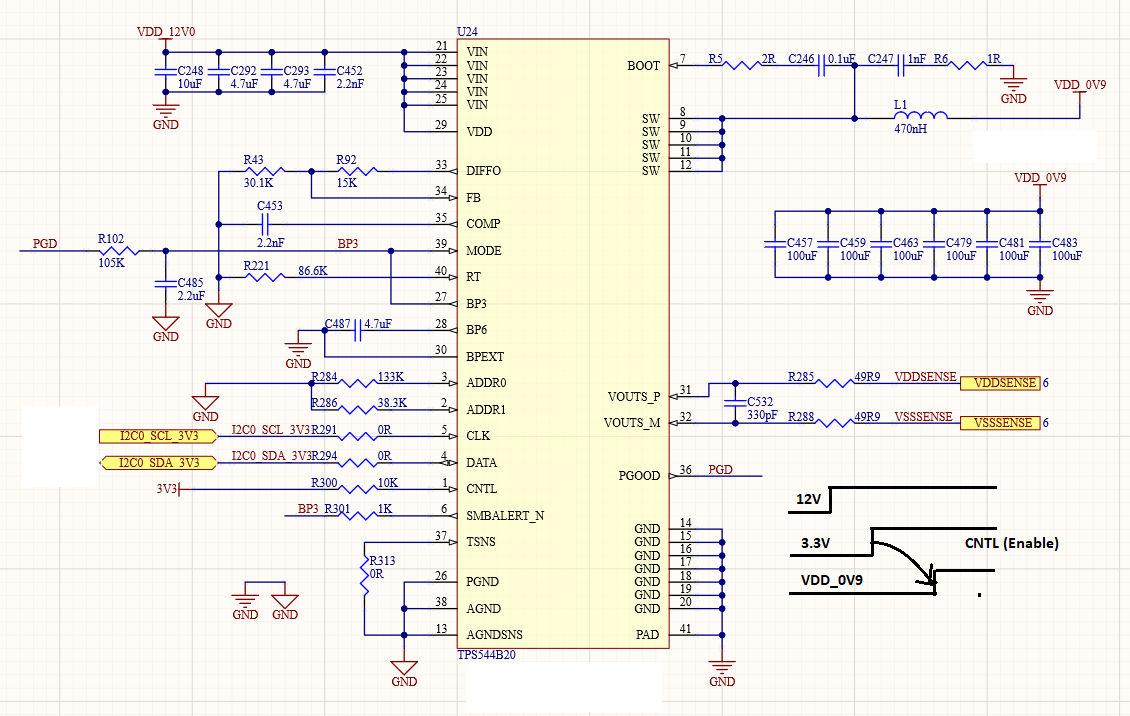

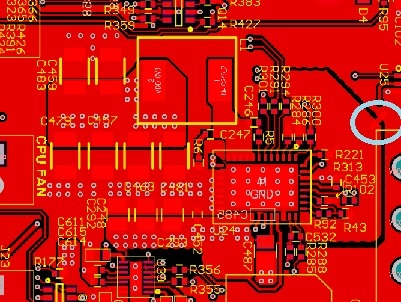

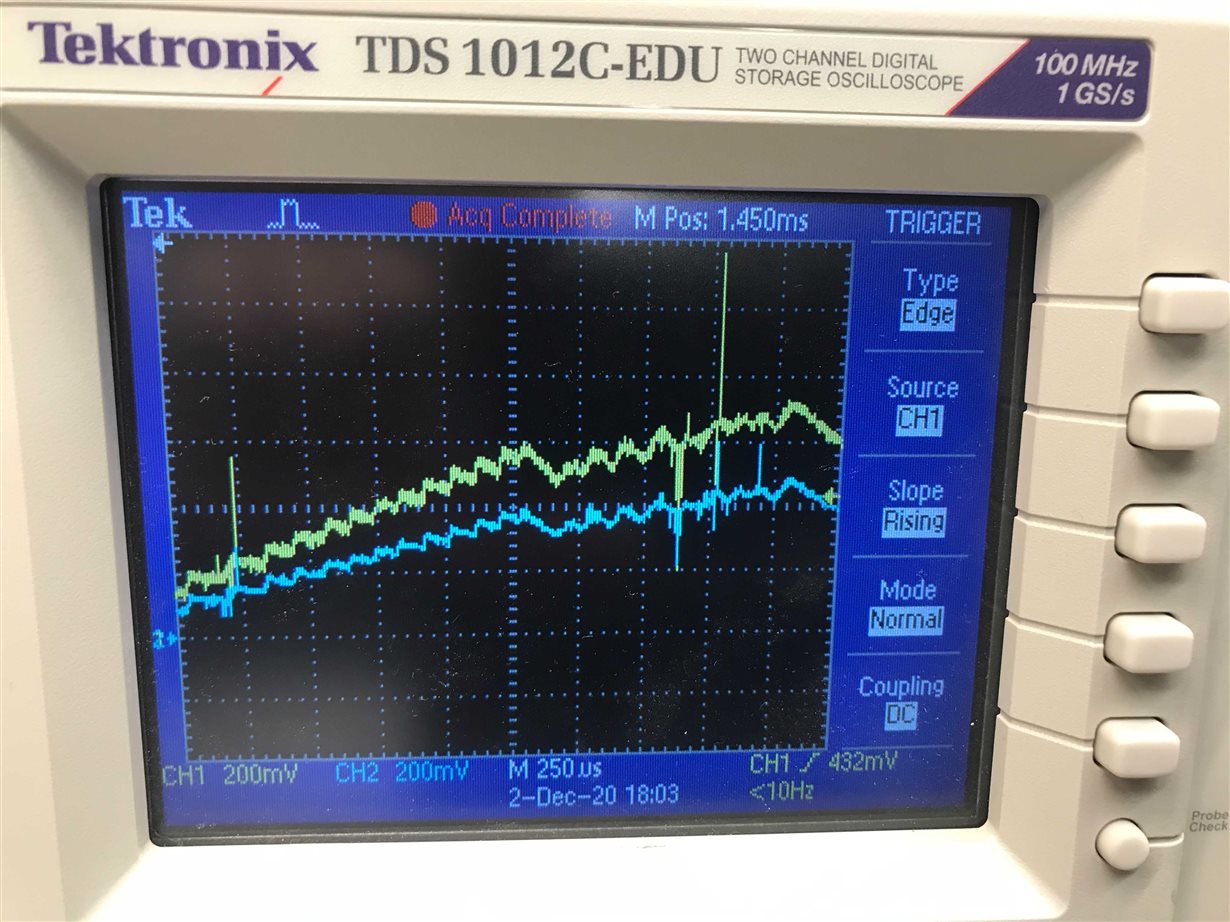

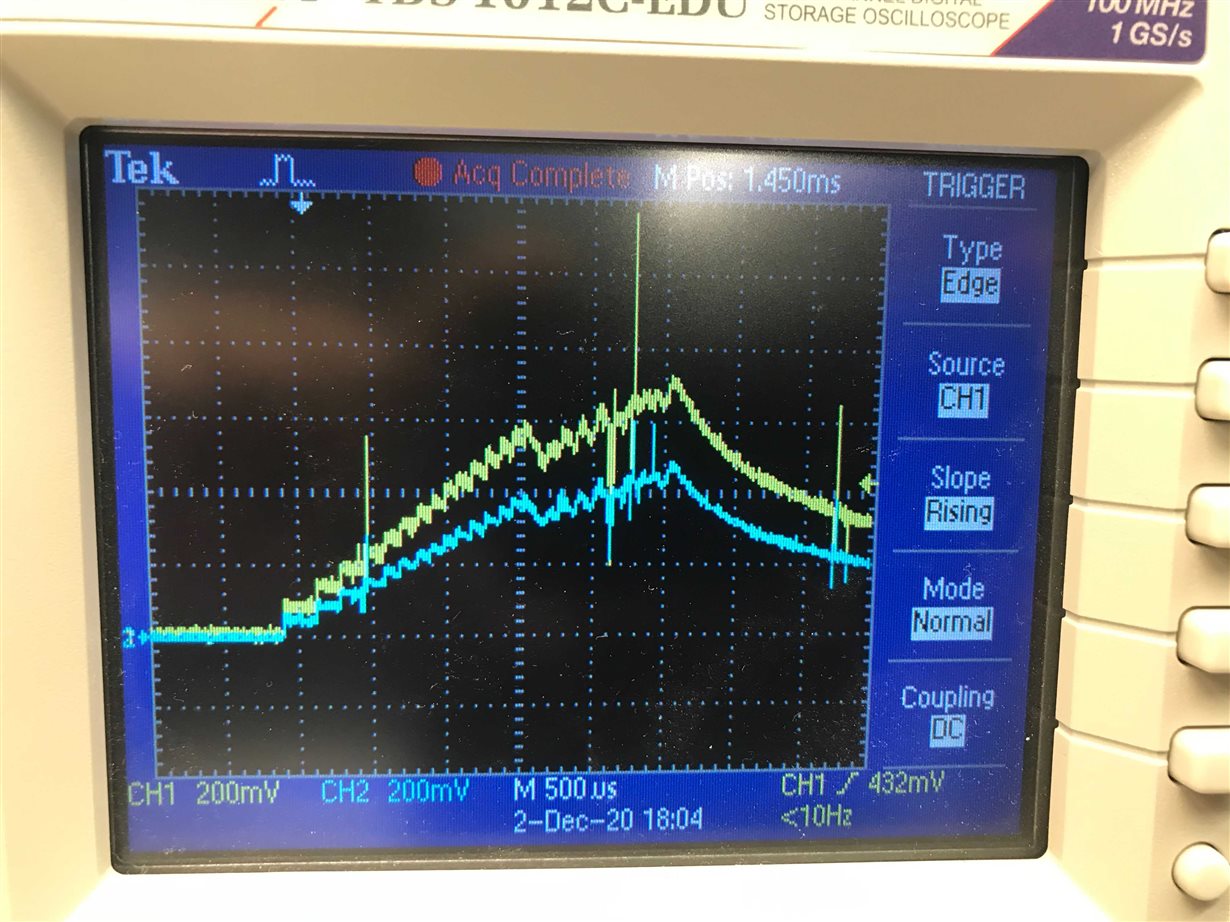

我们使用 TPS544B20作为处理器内核电源(0.9V @ 10A)的稳压器。 原理图是通过 TI Webench 在线工具引用的。 遵循所有布局指南。 可使用 TPS544B20的 CNTL 引脚启用稳压器进行定序。 我们在上电时遇到的问题是稳压器未开启。 我们正在调试该问题、并希望 TI 专家查看原理图并指出观察结果。 CNTL 用于启用稳压器、该稳压器连接到3.3V、10K 作为上拉电阻器、首先连接到 TPS544B20。

请查看原理图并告知我们您的观察结果。

-Naveen