您好!

当 GATE 引脚达到 VGS 阈值并且外部 MOSFET Q1A 和 Q1B 开始导通时、LM5060器件会在启动期间快速将栅极电压拉低。 这种情况反复发生、直到输出电容器充电至输入电压。 下面的第一个波形显示了这种行为、以下波形显示了 EN、OVP 和计时器永远不会达到栅极拉低的条件。

CH1 (黄色)是栅极电压-它充电至大约2.2伏、然后快速放电。

CH2 (蓝色)是输出电压。 输出电压最终达到输入电压(10V)。 侧注:对于较高的电压(~30V)、输出永远不会稳定。

CH1:OVP 引脚上的电压。 对于 OVP 触发、电压保持远低于1.6V 阈值。

CH1:EN 引脚上的电压。 EN 保持在2V 使能阈值以上。

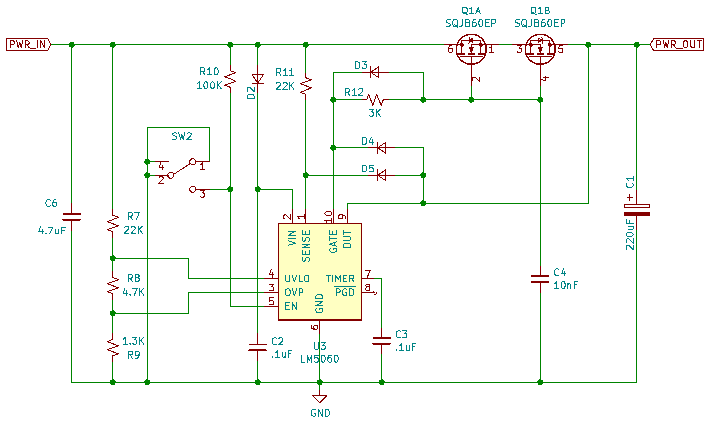

由于没有记录的栅极拉低的原因、我怀疑栅极电压由于噪声耦合到 LM5060 电路而拉低。 我在高频噪声最可能的位置添加了电容:MOSFET 的源极引脚(下面的 C5):

借助于这个额外的电容、源极引脚的转换率和相关的噪声被减少、并且栅极引脚不会拉低。 输出电容器按预期充电:

在 Q1A 的 VDS 上添加电容器不是一个安全的解决方案:如果将30V 电源热插入器件、则源极节点将上升至30V、而栅极保持为0、并且将超过 VGS 最大值。 我也尝试了从源极到接地的电容-但这通过将更多噪声耦合到 LM5060使情况更糟。 这可能适用于巧妙的接地路径布局。

此噪声耦合和栅极引脚放电是否是 LM5060的已知问题? 是否有任何其他方法可减少噪声耦合或消除此启动栅极放电的建议?

谢谢!