我们有一个可严格复制 LM5060EVAL 设计的电路板。

我们的 OVP 略高、为62V。 当我们将电压升高到该阈值时、LM5060会正确跳闸并关断 FET。 但随后它继续让它冒烟... 引脚2 (VIN)的明显损坏。

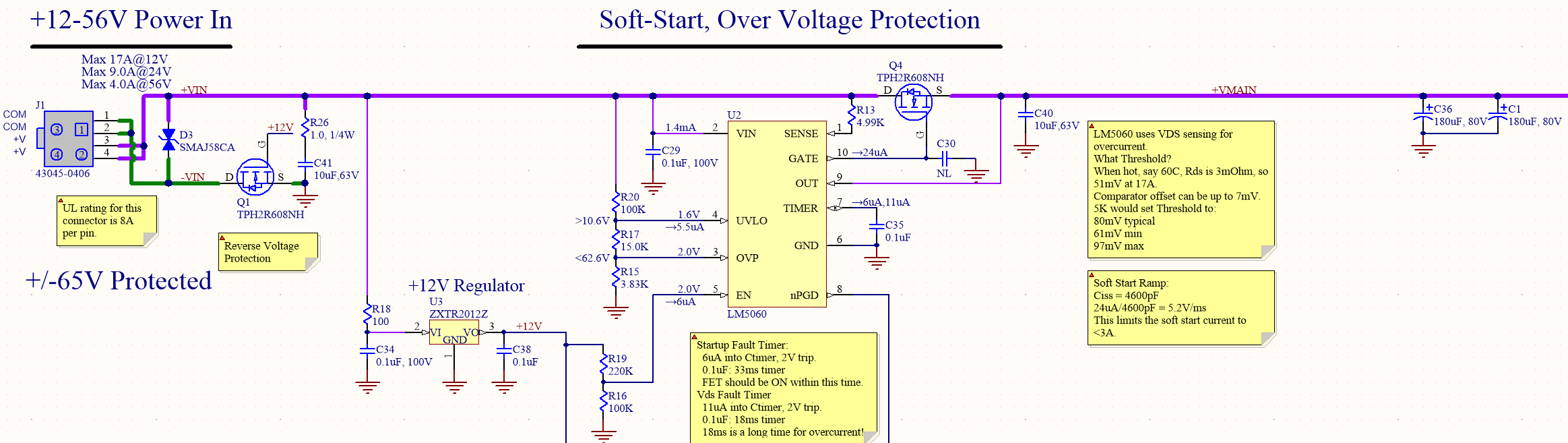

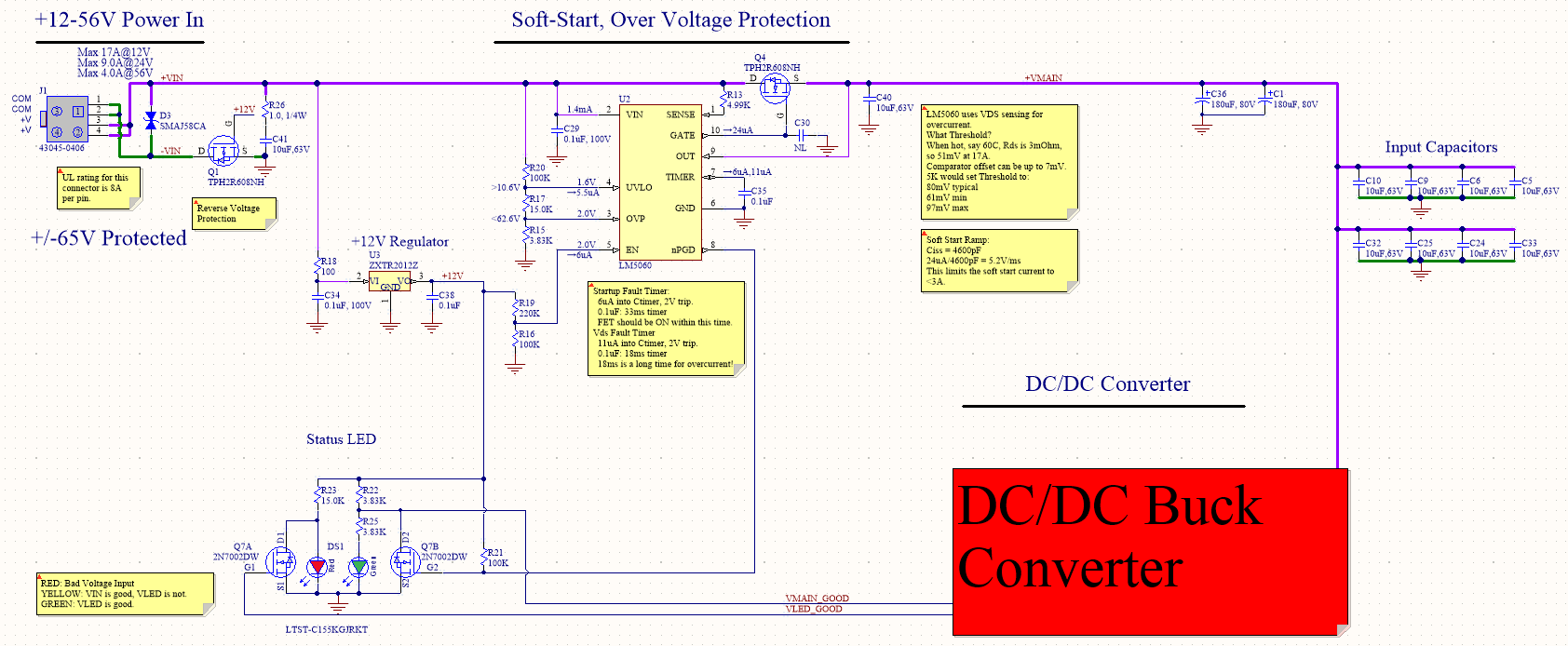

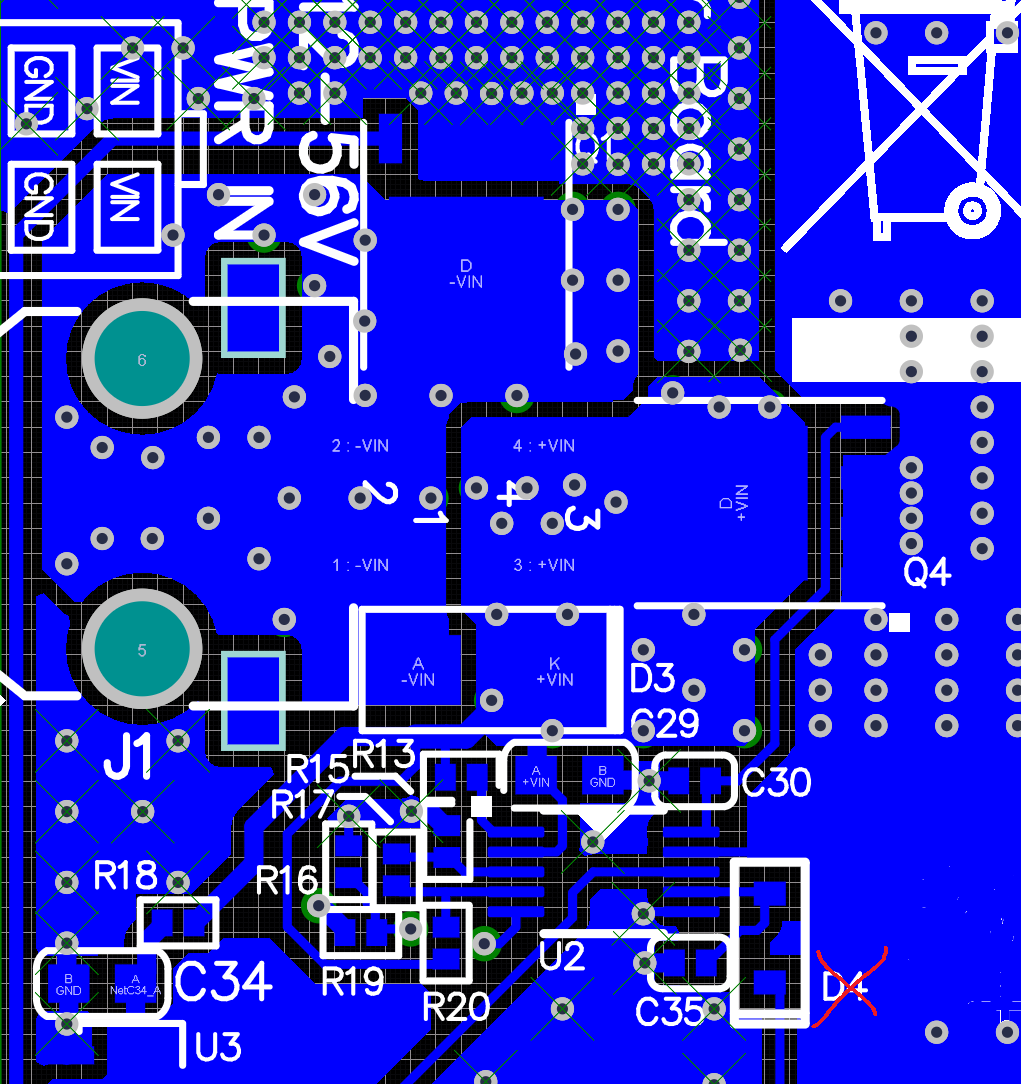

我们已经尝试了很多东西、但对这里发生的事情却是一种损失。 以下是我们的原理图摘述:

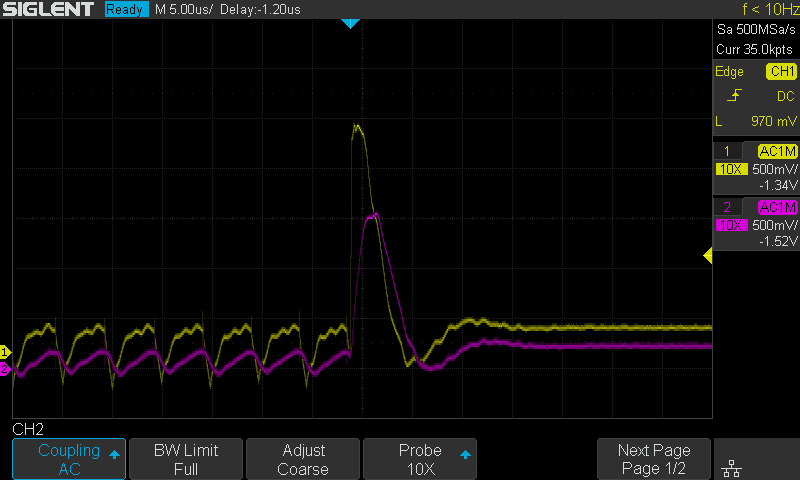

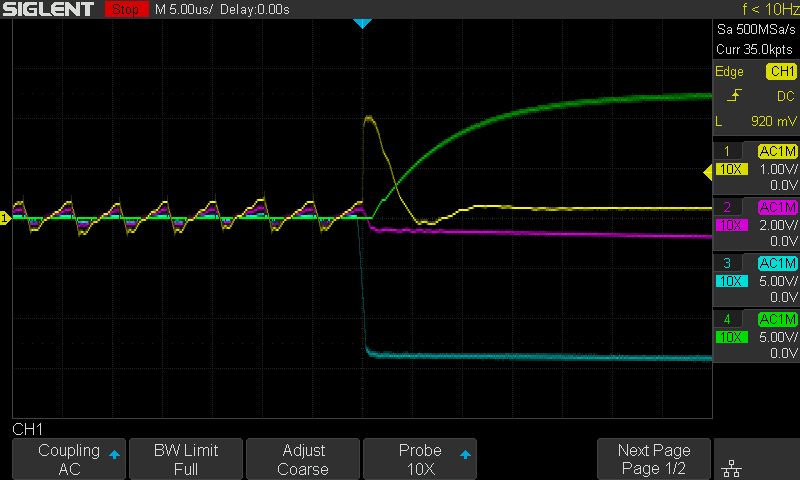

我们已经完成了数十个 LM5060的工作、试图解决这一问题。 负载的问题似乎更严重、但这不是必需的。 当发生 OV 跳闸且电感反冲仅为几伏时、我们有+VIN 和+VMAIN 的示波器捕获。 另一个可能的线索是、nPGD 信号(100K 上拉至12V)会进入2N7002 FET 的栅极、该 FET 通常在故障后损坏。 当 LM5060发生故障时、较高的电压可能会漏电 nPGD?

但最奇怪的观察结果也是最具可重复性的:当+VIN 升至63V 时、全新的电路板首次尝试熔断。 然后、我们更换 LM5060、电路板永远保持良好状态。 新型 LM5060始终能正常工作、并且绝不会再次出现故障。 我们不能对这一看法作出解释,但它已经重复了很多次。 这有什么意义吗?

谢谢!