虽然标题很直率、但不幸的是、正是发生的情况、但芯片最终导致输入短路。 现在、这是一个真正的担心、因为我已经为两个即将推出的产品做好了准备。 对于一个原型、我有其中的5个芯片、昨天的第3个芯片、我被立即爆炸的第4个芯片取代、现在我已经在第5个芯片上工作了。 一旦烧断、输入测量值为0.04欧姆、因此会直接短路。 内部 FET 出现故障。

情况

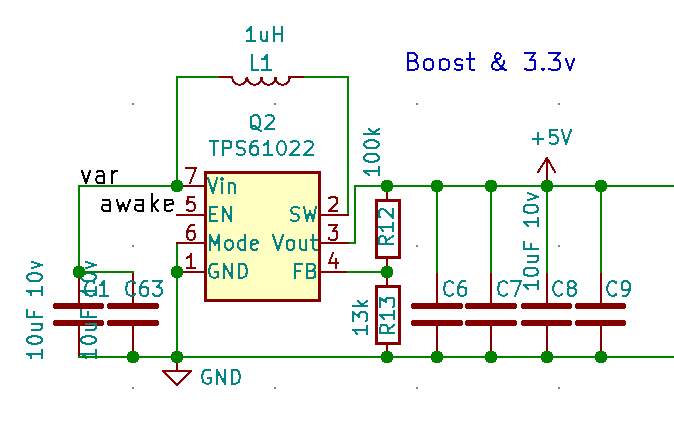

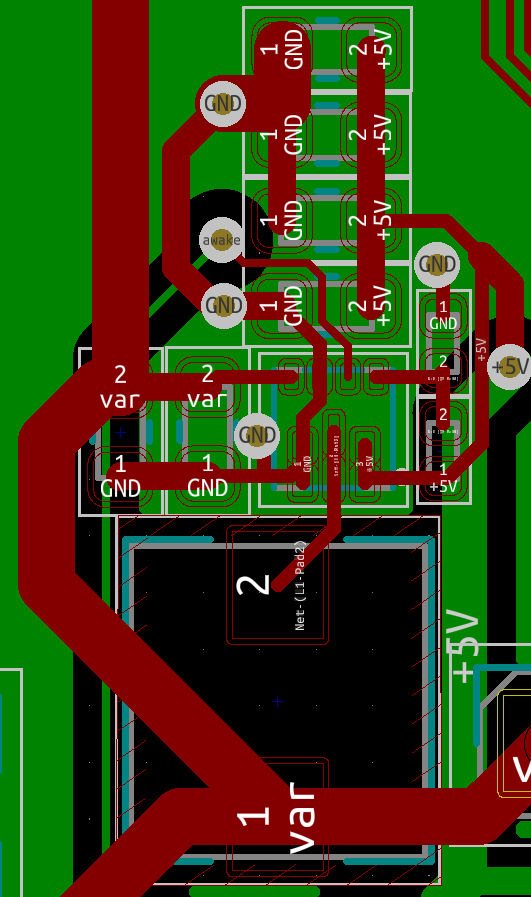

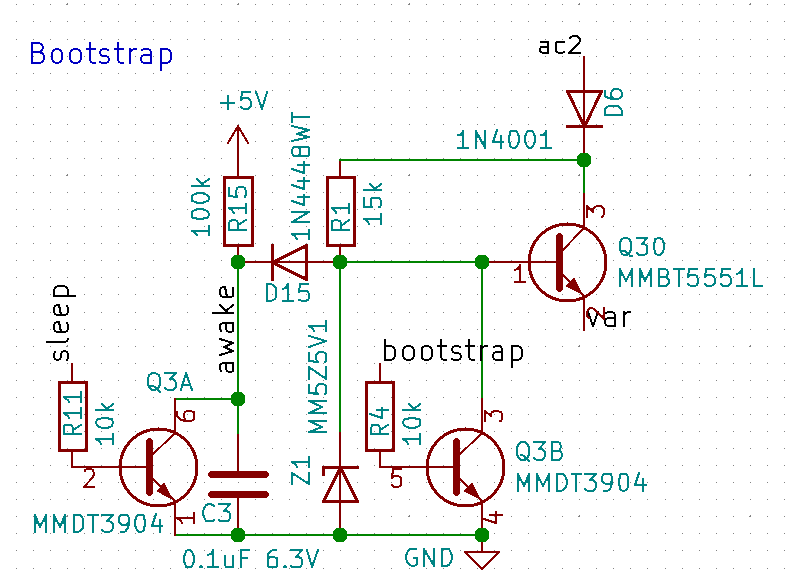

TPS61022目前仅通过50mA 的限流电源对电压进行升压(这将第4次爆炸)。 作为自举操作的一部分、输入电压最终约为3V、而 EN 引脚最终等于输出或高于输入约+0.4V。 这最好用原理图来显示。

AC2目前是6.5v DC 50mA 电源。 没有负载(或最大值约为10mA、因此 TPS 的输出基本上没有负载)。 Vdd 电压为"var"。 EN 引脚连接至"唤醒"状态。 TPS "5V"的输出锁存 EN 引脚。 一旦将压降计入其中、TPS Vdd 上的电压降约为3.5V。

5551的压降约为1.2V、1n4448约为1V、因此 EN 引脚在启动时可能略高于输入电压。 数据表中没有任何内容可以说这是不允许的、但这是我可以想到的唯一事情、值得确认。

电路本身工作正常、升压至5.25V。 我没有尝试任何实际负载、因为我的主要目的是弄清芯片为什么会不断损坏自己。