请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

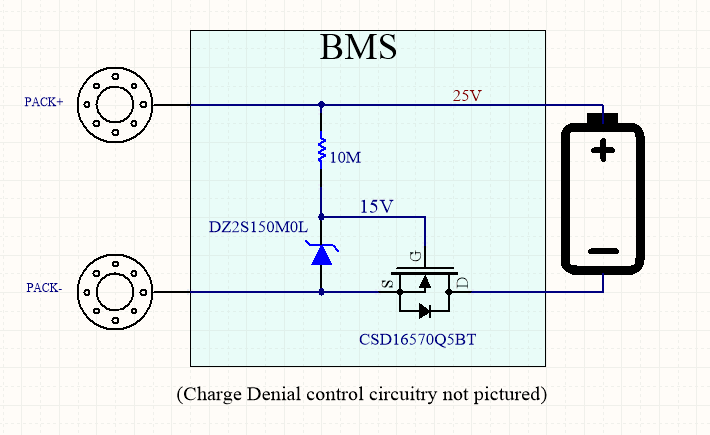

器件型号:CSD16570Q5B 我正在为 BMS 设计低侧 CHG 拒绝开关。 MOSFET 的源极侧将暴露在外界环境中。 我目前正在使用15V 齐纳二极管连接到栅极、并通过弱上拉至 PACK+来驱动栅极高电平、并使用我自己的电路将栅极拉至低电平以关闭 MOSFET。 简化电路如下图所示。

虽然 Vgs 通过齐纳二极管受到 ESD 事件到 PACK-但我担心 MOSFET 关断时由于 ESD 而导致的 VDS 违规。 我在那里似乎找不到任何有关这方面的文献。

当涉及 ESD 事件时、VDS 违反通常是需要关注的问题、还是 Vgs 通常是唯一需要保护的问题?

在所示的示例中、如果在 PACK-上发生-8kV 事件、而 FET 处于关断状态、那么我预计会看到8kV 的 VDS。 显然、这会违反数据表中的绝对最大额定值。 虽然时间很短、但是否仍会发生损坏?

如果这是一个问题、FET 上的齐纳二极管是否可以解决这个问题?