您好!

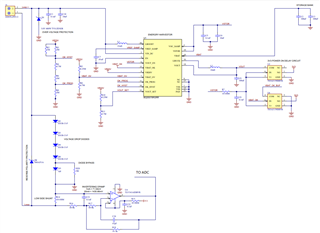

我们尝试在4-20mA 设计中使用 BQ25570、并将此设计用作参考: https://www.ti.com/tool/TIDA-00649

VSTOR 输出的稳定性有问题、稳压电压为5V、但通常情况下、VSTOR 输出会达到6.5V 的尖峰、VBAT 输出也会出现相同的尖峰。 在此尖峰期间、我们看到 VBAT_OK 信号变为低电平、VOUT 输出开始下降。 如前所述、电路板由4-20供电、当我们将电流增加到接近20mA 时、尖峰会变得更加普遍、当我们降低到4mA 时、尖峰仍然会发生、但变得不太普遍。

问题在于电流较高、当这些尖峰确实经常发生时、我们的3.3V VOUT 下降到如此低、以至于我们的 CPU 每隔几秒或更频繁地复位一次。

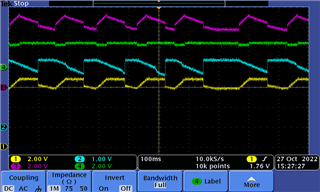

VSTOR 的外观如下所示:

这里是当尖峰频繁发生时 VOUT 的样子:

最后是我们的原理图:

是否有任何关于问题可能是什么的想法? 我们尝试使用不同的电容值,似乎无法完全解决问题:/。 我们确实发现、如果我们通过在该线路上放置一个小电容器来破坏 VBAT_OV 读数、或者问题"消失了"、但实际上似乎会发生的是、它会将读数拧得更松并将 VSTOR 固定在6V、 但这可能是某种线索?

如果有任何意见,我会非常感谢!!!

谢谢、

Jarrod