请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:CSD87350Q5D 大家好、

对于 CSD87350、TI 说这针对5V 进行了优化。 这是否意味着驱动器 IC 的 VDD 为5V?

对于某些应用、VDD 为5V。 但有一个由自举二极管引起的压降。

如果 VGS 的电压低于4.5V、会对其产生什么副作用?

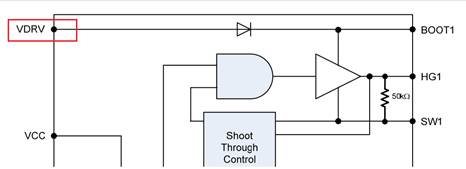

下面是一个在 VDRV 上施加5V 电压的示例、但对于高侧 FET、VGS 将<=4.5V。

谢谢

请求