主题中讨论的其他器件:AM3358、

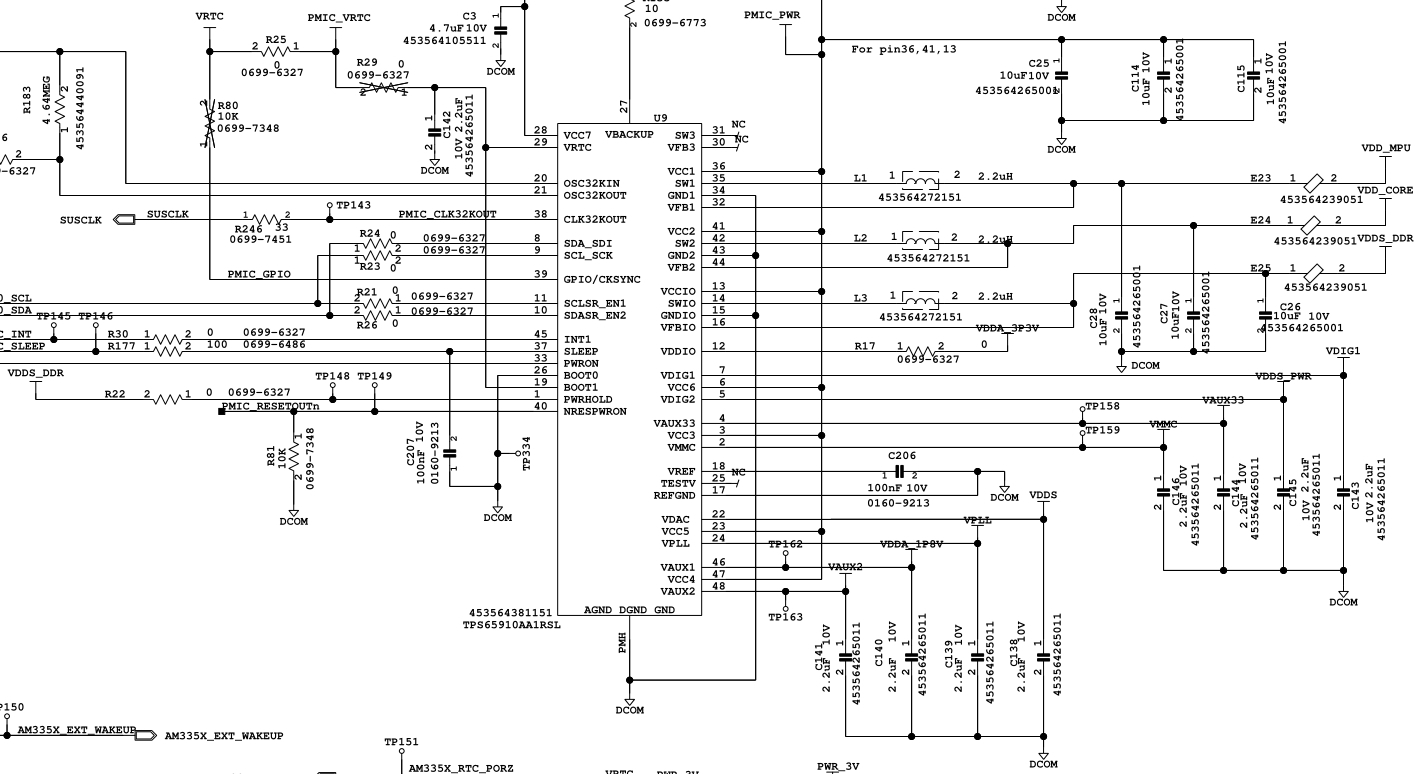

大家好、我们将 PMIC 从 TPS65910AA1更改为 TPS65910A3A1、以便在现有产品上支持 DDR3器件。 PWRHOLD 引脚连接到当前产品中的 VDDS_DDR (SWIO 输出)、如下图所示、我们在更改后意识到 PWRHOLD 的 HI 电平裕度会变小、因为 VDDS_DDR 从1.8V 更改为1.5V。

我们对将 PWRHOLD 连接到 VDAC 输出的当前产品进行了实验、但系统无法成功断电。 只有我们更改为 VAUX33、系统才能关闭。

您能帮我了解行为原因吗?