主题中讨论的其他器件: TIDA-01540、 UCC21220

各位专家:

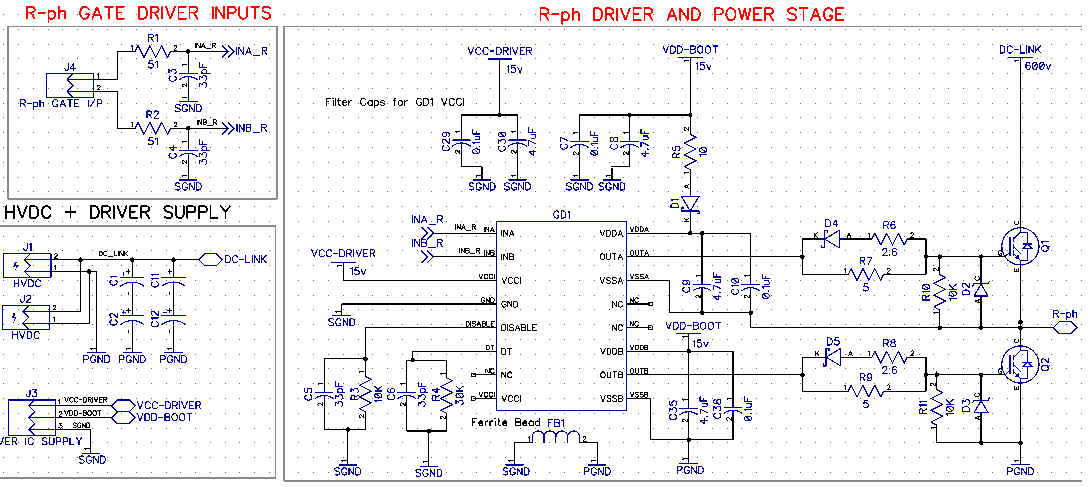

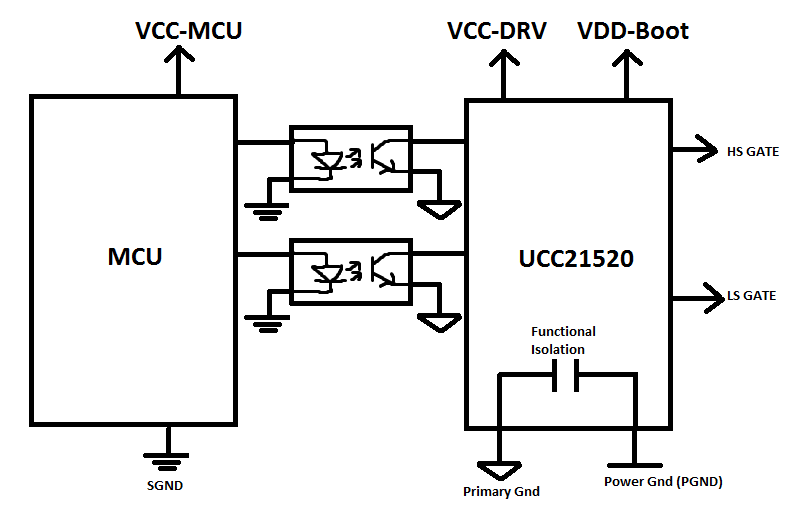

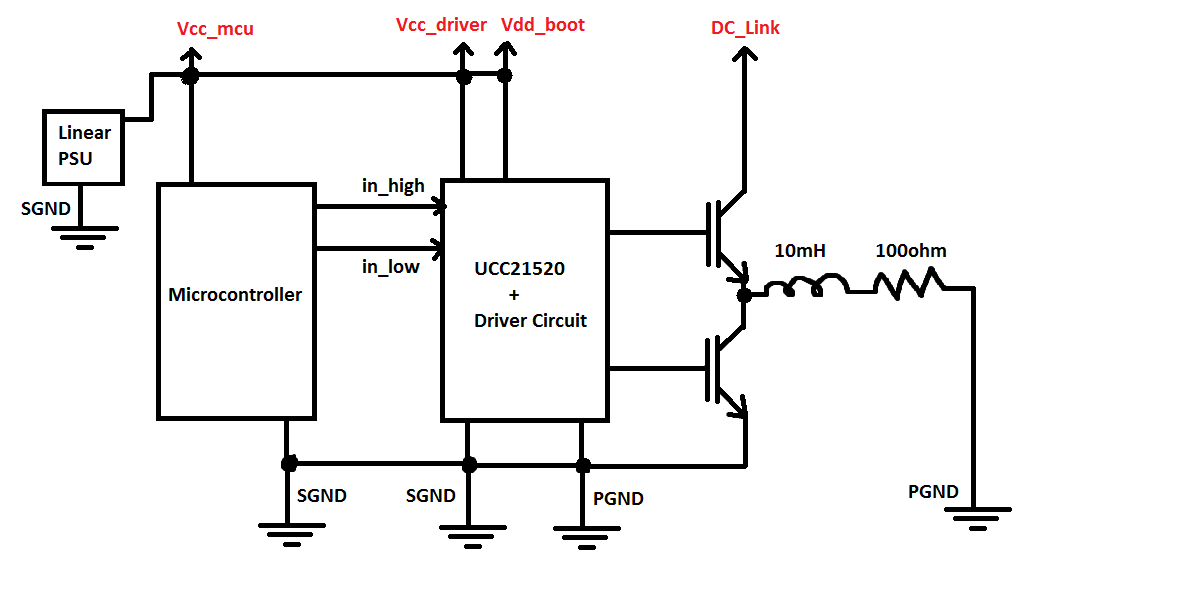

我使用 UCC21520来驱动三相逆变器的一个桥臂。 系统的方框图是-

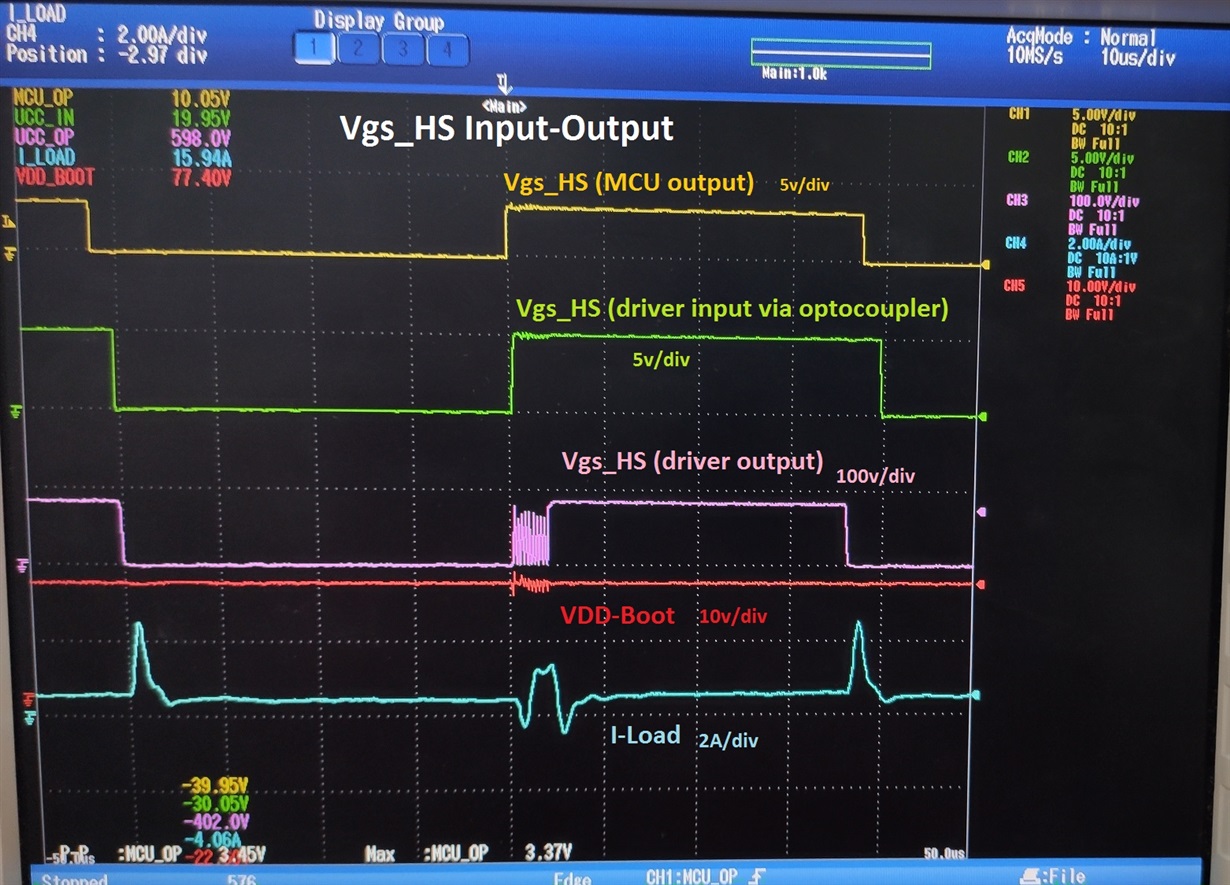

当未连接负载且直流链路= 0V 时、高侧和低侧栅极脉冲是完美的。在无负载情况下、随着直流链路增加、超过30V、我开始听到来自栅源环路的奇怪噪声。 我无法识别原因、但这种现象也在其他阶段发生。 Hum 的振幅随直流链路的增加而增加。 它听起来像是 HF 正弦信号。

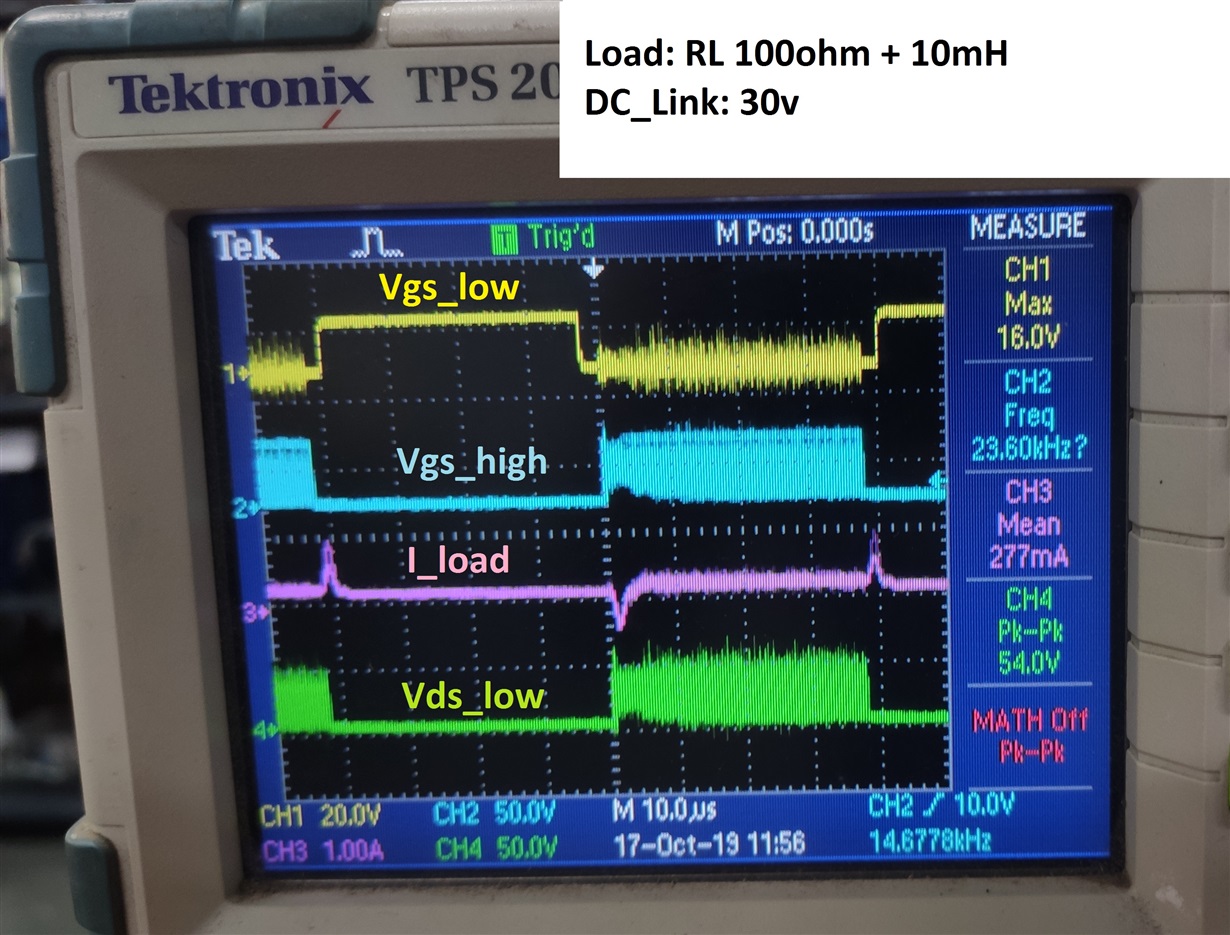

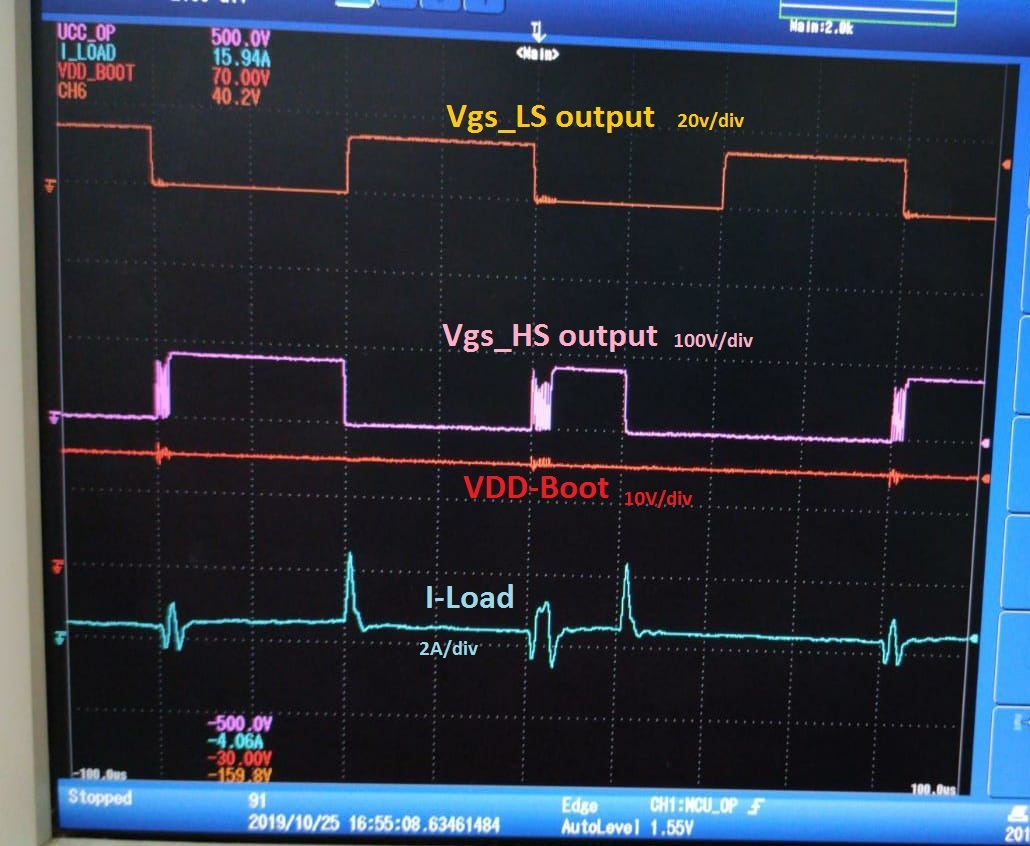

连接负载时、情况会急剧变化。 在~30V 直流链路、10mh+100ohm RL 负载下、高侧栅极脉冲会失真、在开通期间在高电平和低电平之间快速切换-

VG_HIGH 以 wrt GND 为基准。

这种现象仅在高侧导通期间发生。

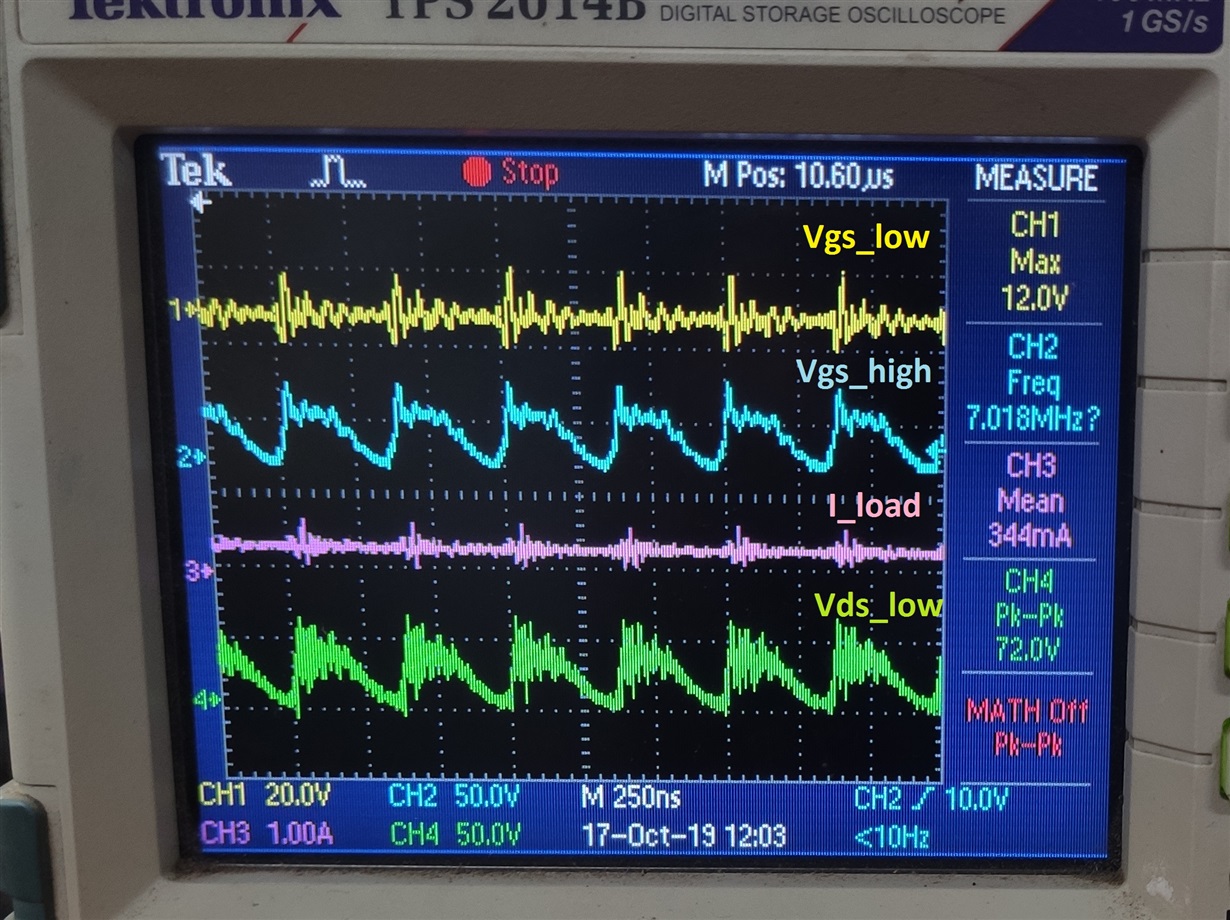

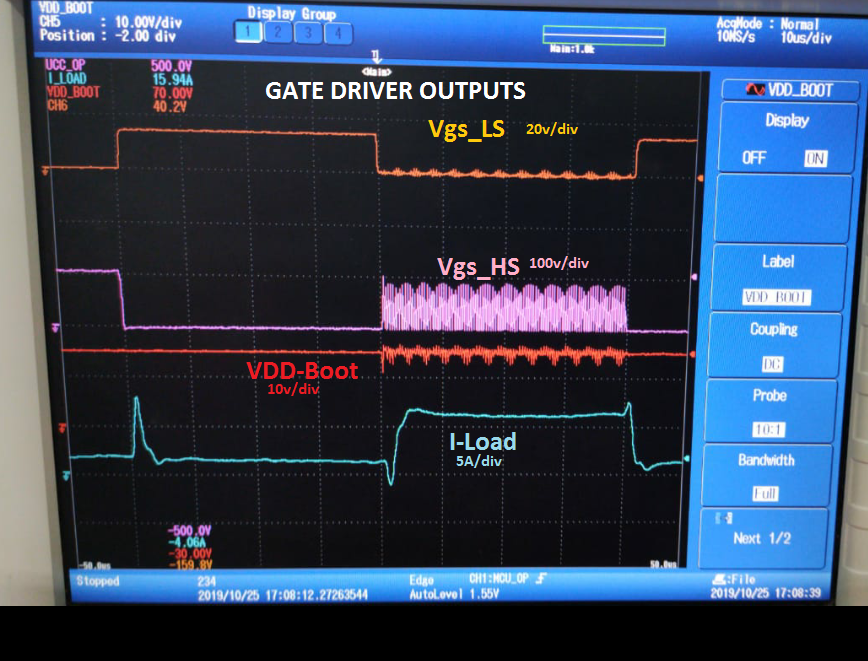

放大波形。

在30V DC-Link、100ohm+10mH 负载下会发生此失真。 随着负载电阻的增加、在较高的直流链路级别会发生失真(这是否与负载电流有关、di/dt 问题可能存在?)

令人惊讶的是、相同的失真会在 MCU 端得到反映。 MCU 的电源会以相同的方式失真。 我尝试更改为新的 MCU 板、在 MCU 的 LDO 和 VCC 引脚上放置旁路电容器、但问题仍然存在。 (那么、驱动器本身的输出级可能会导致问题?)

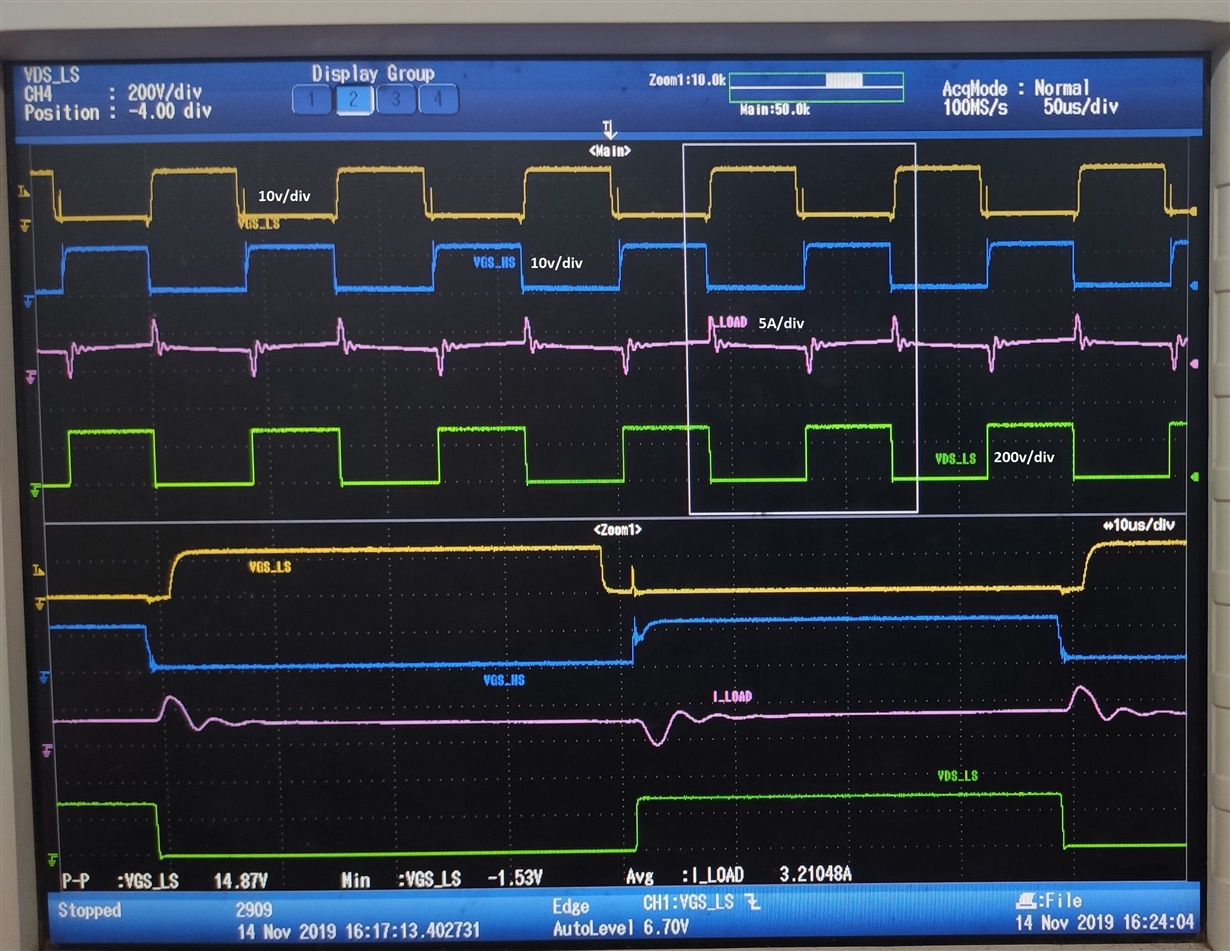

出于好奇、我进一步提高了 DC_Link。 随着直流链路不断增大的噪声强度、在某个点、噪声会停止、驾驶员突然开始像这样古怪地行为-

e2e.ti.com/.../driver-fail.mp4

(此处更改了颜色方案、抱歉)

黄色=高侧(wrt 至 GND)

蓝色=低侧(wrt GND)

即使在多次复位之后、驱动器现在仍然始终以视频中所示的方式产生高侧栅极脉冲。 现在、当负载= 100欧姆+ 10mH 时、这种情况在 DC-Link <15V 时发生。 在同一导通周期中、驱动器最初会产生适当的高侧栅极脉冲、然后在剩余导通时间内发生故障。 这种情况定期发生、仅在高侧发生。 低侧脉冲非常完美!

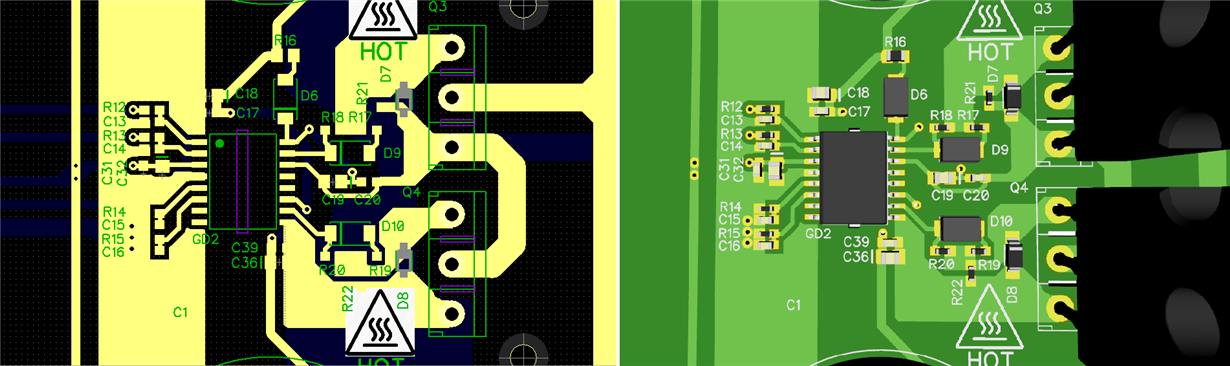

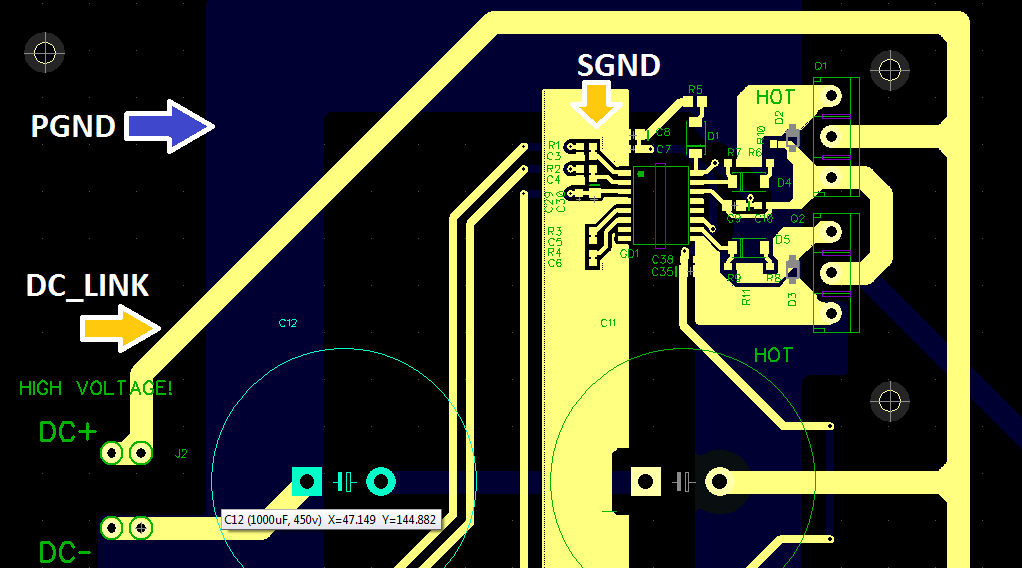

这是我的电路板布局的一个片段-

栅源布局

直流链路布局

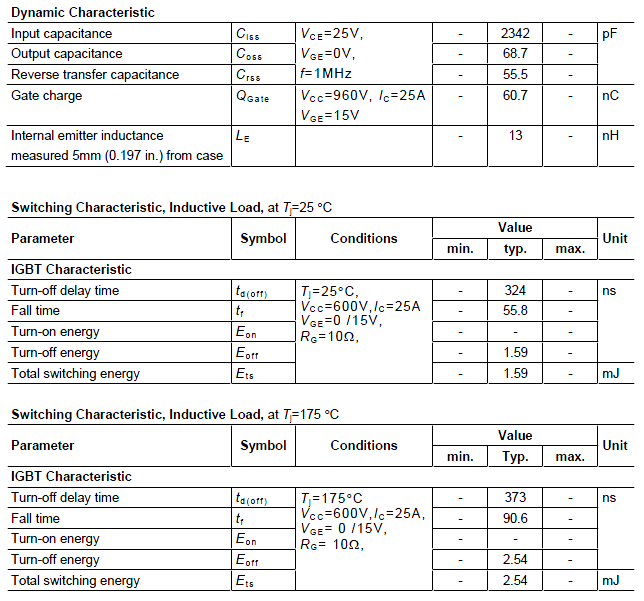

IGBT 电容

根据输入电容和栅极电荷、Cboot 的选定值远高于建议值。 我无法量化高侧故障的原因。 失真发生在驱动器级、并反映在微控制器板中。 我已分别路由 PGND 和 SGND、并仅在一点处将其短接(未显示在上面的布局中)

那么、是什么导致了问题呢? 如何解决问题? 我