大家好、

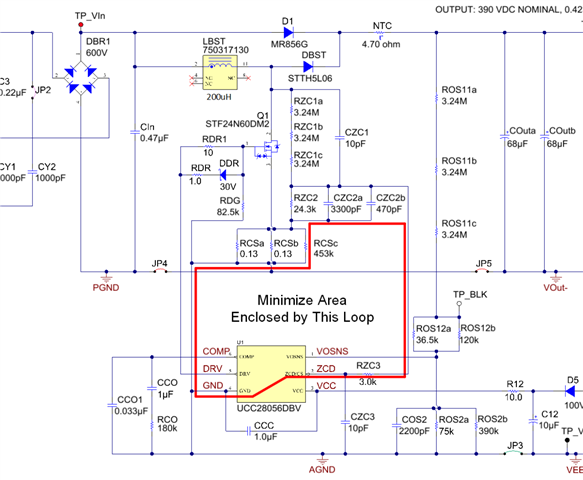

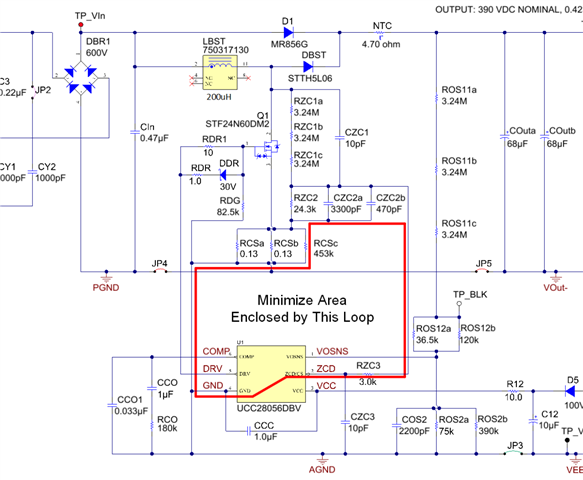

数据表建议该环路较小以防止磁性拾取、我是否可以知道较大的环路为什么会有噪声拾取?

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

数据表建议该环路较小以防止磁性拾取、我是否可以知道较大的环路为什么会有噪声拾取?

谢谢

您好、Fred、

ZCD/CS 正在监控两个关键信号。 当 DRV 引脚为低电平时、 ZCD 输入将监控 电感器零电流转换。 任何增加的迹线电容都将引入相移以及电容滤波的衰减。 这将导致 过零检测错误、导致 FET 在非最佳点打开。 当 DRV 引脚 为高电平时 、CS 输入会监控相对于 GND 的小电压、因此任何添加的阻抗都会导致电压偏移、这将影响 电流测量的精度。 通过最大程度地减小 ZCD/CS - GND 环路的环路面积、可以最大限度地减小寄生电容和阻抗、从而减少这些误差。 减小环路面积还使该敏感区域成为更小的天线接收器、并增大其与功率级和磁性元件中产生的开关噪声的距离。

此致、

射线