Other Parts Discussed in Thread: TPS7H4010EVM, TPS7H4010-SEP

您好!

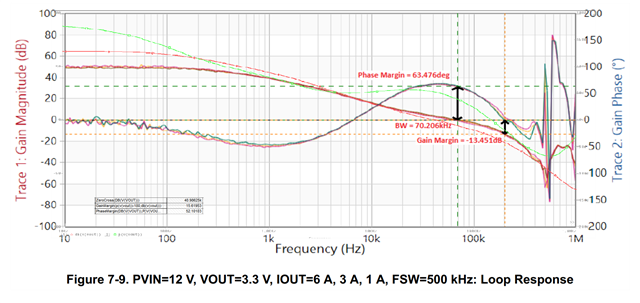

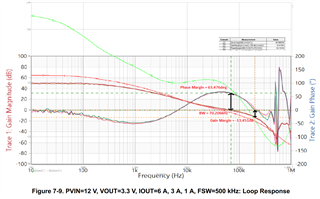

我发现 TPS7H4010EVM 用户指南中给出的环路响应有点难以理解(SNVU744图7-9 P24):

考虑到相位裕度的计算方式、相位偏移是毫无疑问的、因此我预计当增益斜率为0时、相位将大约为180°、而当增益斜率为-1时、相位将大约为90°、但情况并非如此。

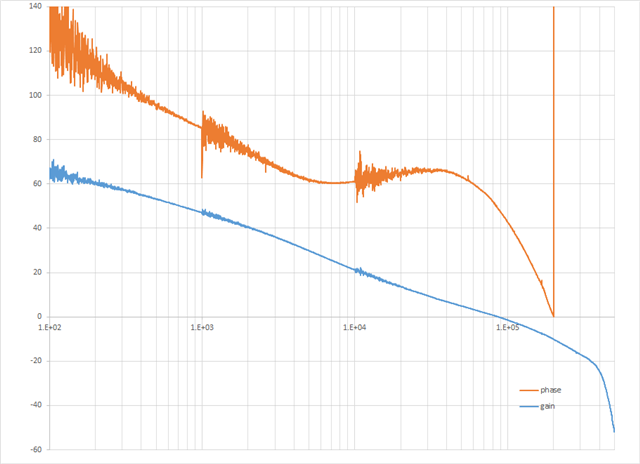

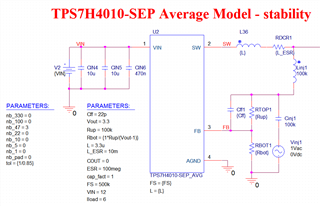

看起来 TPS7H4010-SEP 的平均模型与我预期的模型更加一致,但如果它与实际的转换器不匹配,那就没有太大帮助了:

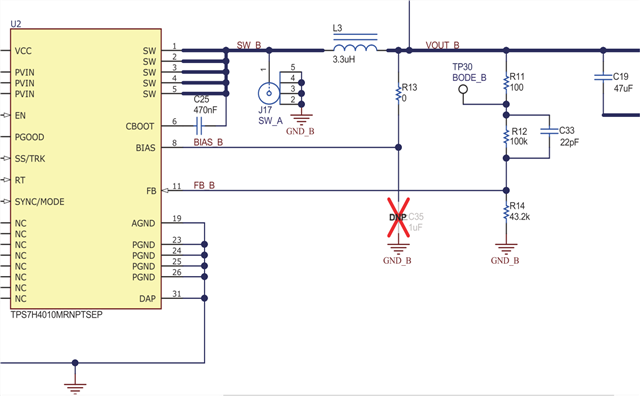

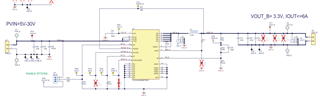

当然,我尝试匹配我的模拟参数(在输出电压上放置3x47uF 电容器):

使用评估板上的实际内容:

错误在哪里?

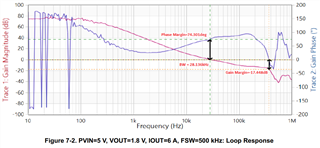

还应注意的是,评估板的1.8V 侧在用户指南中给出了一个更接近我预期的环路响应(图7-2 P20):

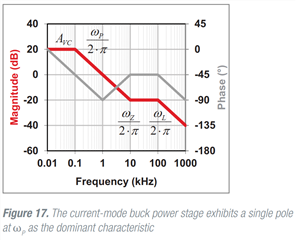

在1k-10kHz 范围内仍有-2增益斜率,我认为它与标准电流模式降压转换器不匹配,如 slup340图17 P10中所述:

谢谢、