主题中讨论的其他器件: TPS54233

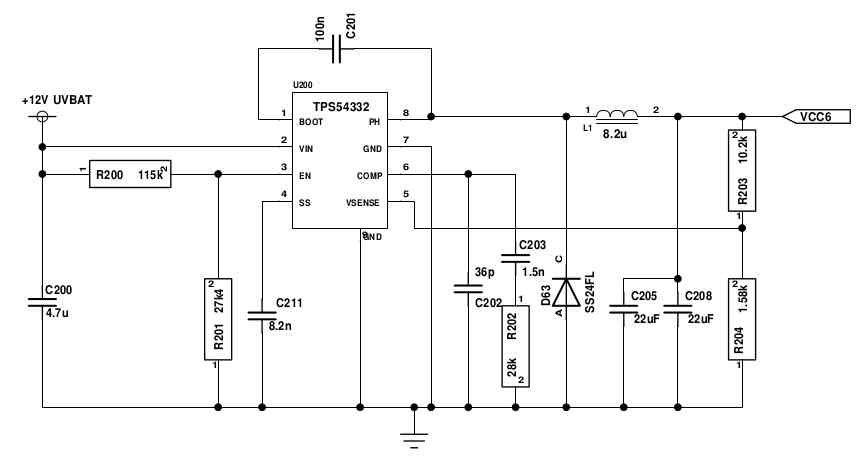

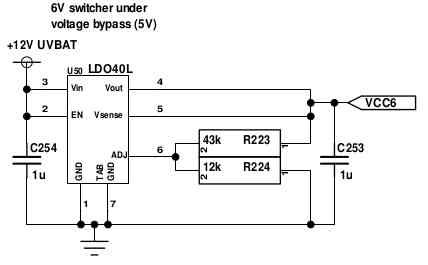

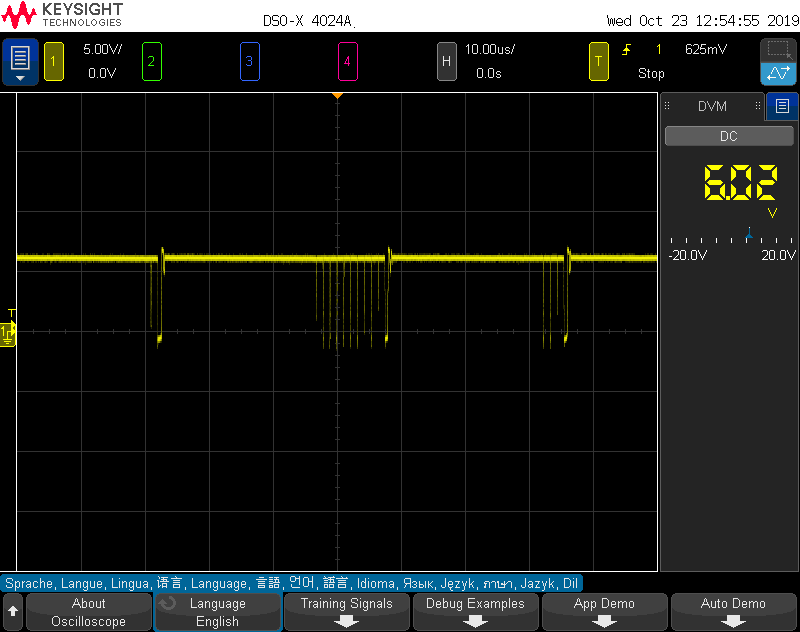

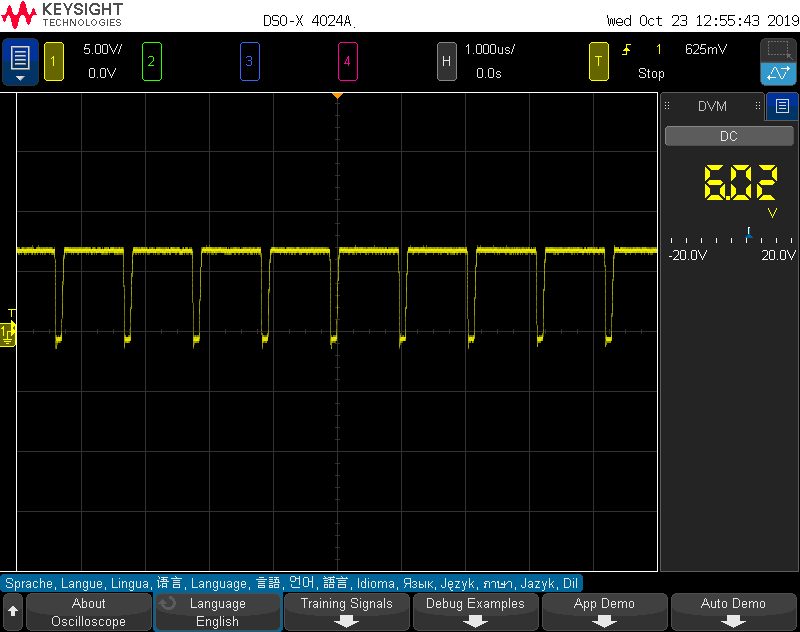

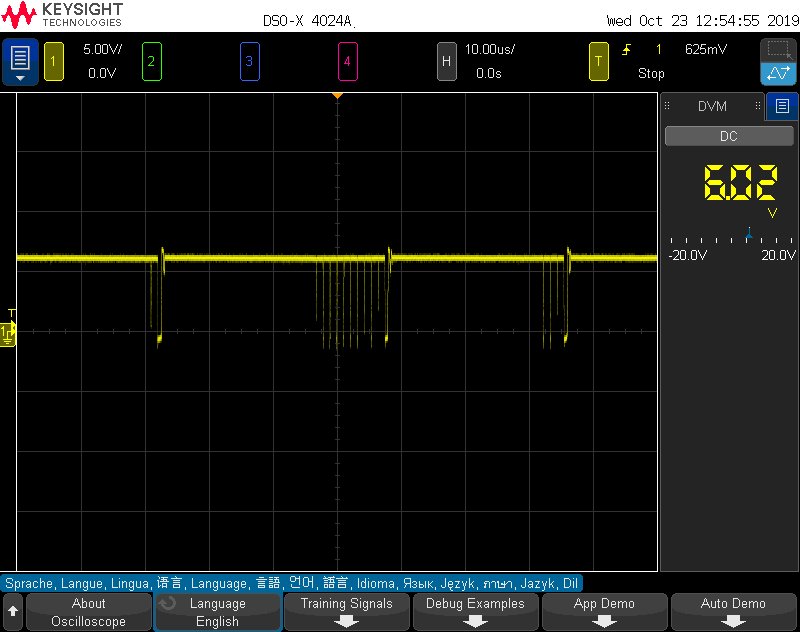

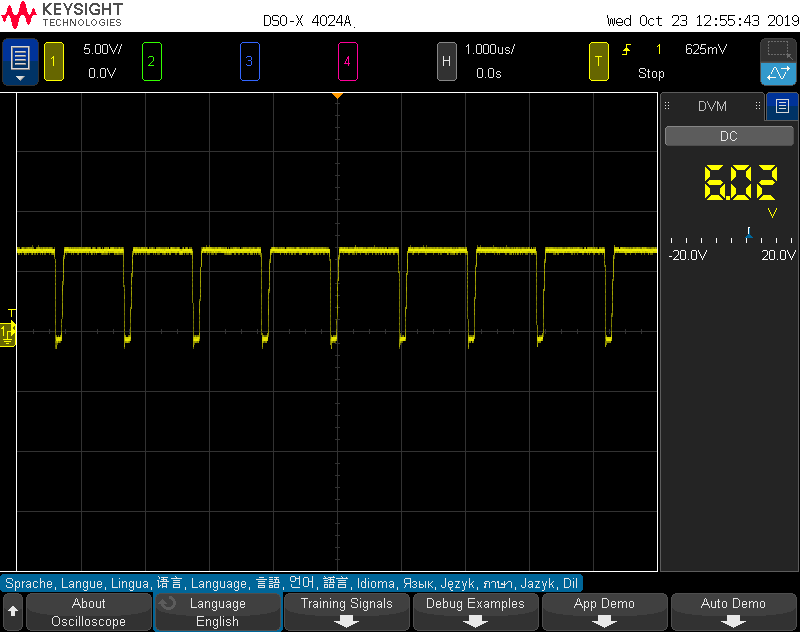

我在使用 TPS54332作为6V 电压轨的主稳压器、但使用5.5V LDO 稳压器备份的电路中看到了一个奇怪的现象(因为 TPS54332不想在100%占空比/直通模式下运行)。 当输出轨已处于5.5V 时、使能阈值似乎向上移动-例如、在使能引脚上具有1.701V 电压时、尽管数据表中的典型使能阈值为1.25V、最坏情况下为1.35V、但 TSP54332仍然不会导通。

此预期行为是来自器件还是仍应尝试在1.25V 使能电压下启动?

如果是预期的、那么是否有一些文档/设计信息可用于预测实际的使能阈值?

此致、

Patrick Herborn。