请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:CSD17308Q3 尊敬的:

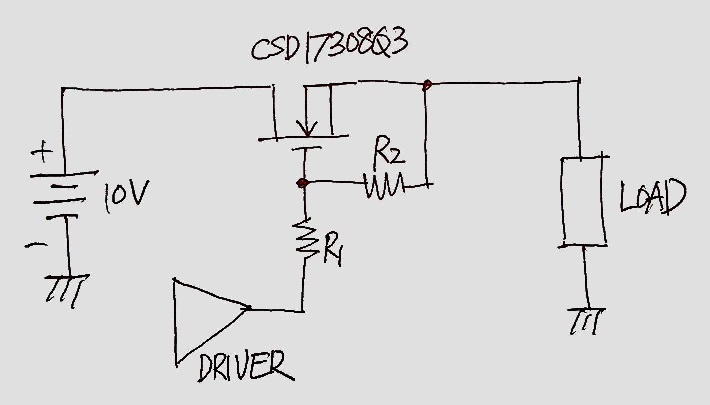

如图所示、我在电路中将 CSD17308Q3 FET 用于高侧开关、该电路模拟 TI 的驱动器 IC 评估板、其中 R1 = 5k Ω、R2 = 10兆欧。

一个多月以来、我注意到栅极驱动器输出为三态时、有可疑的泄漏电流流经 FET。

您能否保证栅极和漏极之间的电阻器 R2 10MOhm 足以保持 FET 关断状态?

谢谢、

Joshua Kim