主题中讨论的其他器件:AM5716、

您好!

在我的板上有一个 Sitara AM5716及其 PMIC TPS659162RGZR。

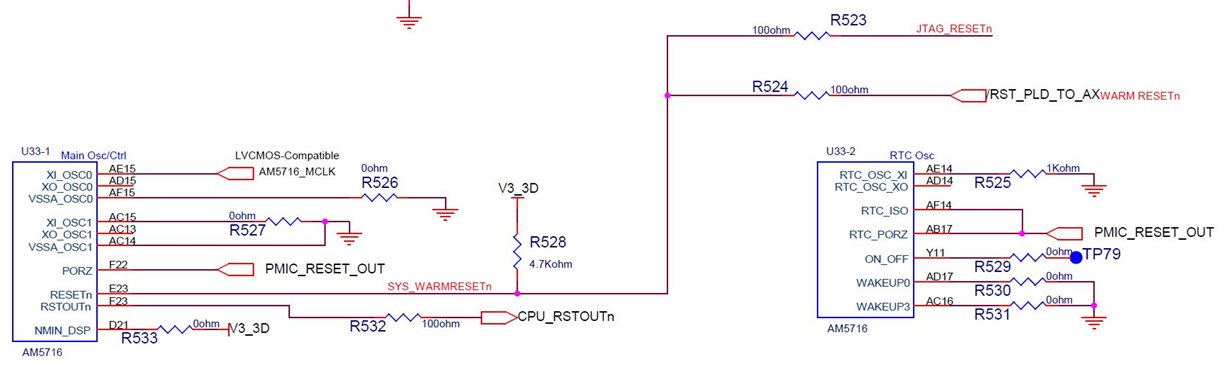

下面我展示了有关 PMIC 的原理图

和复位部分

AM5716_MCLK 是20MHz 时钟、SYS_WARMRESETn 是高电平。

对于连接、我遵循了《为 AM571x 供电的 TPS65916用户指南》(SLVUA04D)中的图2。

PMIC RESET_OUT (Net PMIC_RESET_OUT)和 CPU RSTOUTn (Net CPU_RSTOUTn)始终为低电平(PMIC 的所有电源均正确且 PMIC POWERGOOD 为高电平)。

我放置一个4.7K 欧姆电阻上拉 PMIC_RESET_OUT、该网络和 CPU_RSTOUTn 的行为如下:

从第5.3.4段中的 PMIC 数据表(SLVSD09B–2016年3月–2017年3月修订)中、我读出: "如果从 VCC 到 VIO 的时间小于6ms、则将在 OTP 仍处于初始化状态时提供 VIO 缓冲器、这可能会导致任何 VIO 输出缓冲器上出现毛刺脉冲。 在为 VCC 供电后至少6ms 为 VIO 供电可确保 OTP 被初始化、并且当 VIO 为时、输出缓冲器被保持在低电平

提供。"

因此、我将 VIO_IN 连接到 V3_3D、在3.3V 后上升了26ms、但没有任何变化。

即使 VIO_IN 连接到3.3V、即 PMIC 的 VCCA 电源、所有电源都是正确的。

您能帮我解决这个问题吗?

谢谢你

此致

弗朗西斯科