主题中讨论的其他器件: CSD18537NKCS

您好!

我使用 LM3424使用24V 电池以3.7A 的电流驱动32个 LED (CreeXP-L2、8x4系列并联配置)。

我的问题是、当我以这个电流打开 LED 阵列(J1、J6)时、它会随着时间的推移而开始下降(100mA/分钟)。

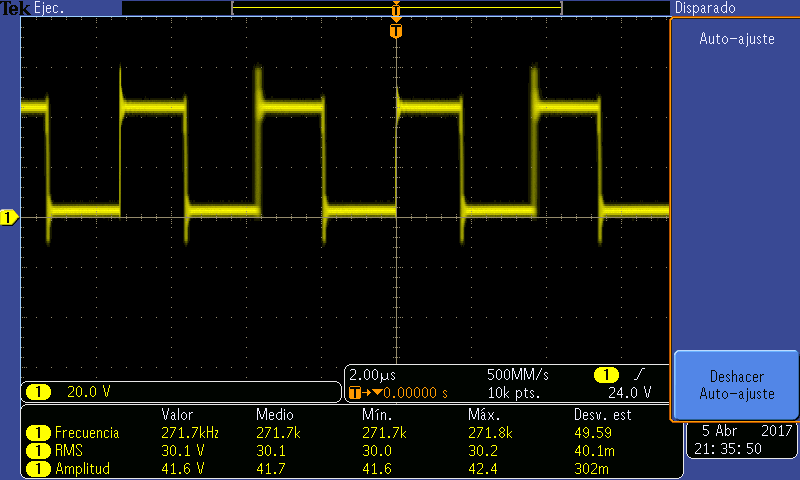

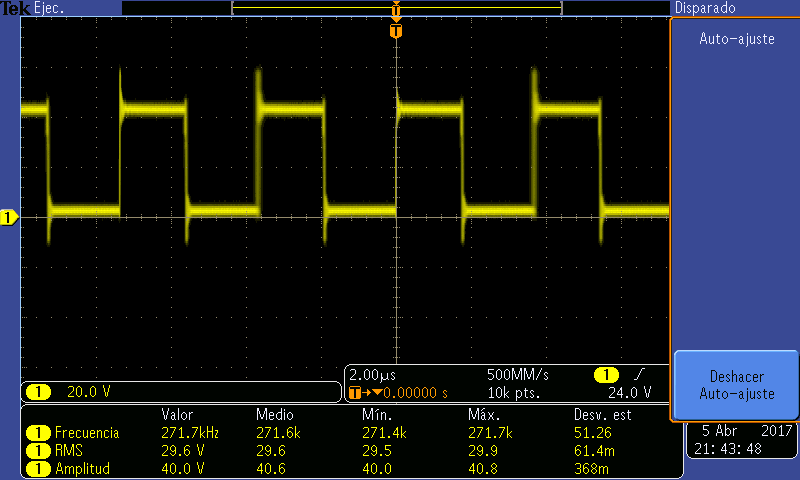

LM3424的工作频率为265kHz、因为 Q1和 D1会发热至地狱(请参阅威胁 https://e2e.ti.com/support/power_management/led_driver/f/192/t/570869)

我的第一种方法是 L1变得过热、LED 阵列也会变热、因此输出电阻会发生变化、因此 LM3424控制环路(R6、R7、R8)使 Q1栅极降低电压?

我测量了 Q1栅极的电压、它开始下降、与输出电流类似。

此外、我使用 PWM 将输出电流降低至1A、以查看行为是否相似。 但在该电流下、它保持恒定(热量更少?)

我附加了原理图以获得更好的参考。 任何建议/意见都是很好的。

提前感谢。