主题中讨论的其他器件:CSD87330Q3D、 TINA-TI、

尊敬的 TI 团队:

我在设计中使用了 TI 组件"TPS51116RGET"来满足 DDR3L 电源要求、并使用了 TI 的 MOSFET "CSD87330Q3D"。

但在过去2周内、我一直尝试对同一设计进行仿真、并观察到以下问题:

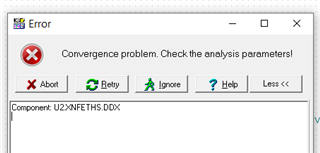

使用 Cadence PSpice:-显示了一些错误,我无法解决(甚至尝试使用未加密的 PSpice 模型) 。 我在这里附加了 PSpice 中的最近错误

e2e.ti.com/.../PSPICE-ERRORESULT.pdf

之后、我尝试了 TINA-TI。 在 TINA 工具上、我得到 VDDQ 输出电压(大约1.35V)和 VTTREF (大约0.675V)。 但 VTT 完全超出范围(低于0.5V)。

我在以下运行条件下获得了上述结果-

VIN= 5V

负载电阻器@Ω VDDQ (SYS_1V35)=> 1 Ω (1.35A)

负载电阻器@ VTT (SYS_1V35)=> 225m Ω (3A)

负载电阻器@Ω VTTREF (SYS_1V35)=> 67.5 Ω (10mA)

请参阅随附的用于仿真的电路图-

请参阅随附的使用 TINA-TI-的上述电路的仿真结果、

e2e.ti.com/.../TINA--WHEN-3-LOAD_2800_RESULT_2900_.pdf

我还尝试了无负载条件、 并获得了以下结果-

e2e.ti.com/.../TINA-WHEN-NO-LOAD_2800_RESULT_2900_.pdf

然后、我还尝试了 S5模式(S5=5V 和 S3=0V)、并得到以下结果:

e2e.ti.com/.../TINA-WHEN-1-LOAD_2800_RESULT_2900_.pdf

如需参考、请参阅随附的我的此组件的原理图设计(SCHEMATIC1_DDR3L.pdf)-

e2e.ti.com/.../SCHEMATIC1_5F00_DDR3L.pdf

请帮我解决这个问题、以便我验证输出电压纹波。

请查看我随附的原理图(SCHEMATIC1_DDR3L.pdf)。

谢谢、此致

Raj Kumar