请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:CSD19534Q5A 主题中讨论的其他器件:CSD18510Q5B

您好!

我正在为该 MOSFET 设计封装、以便将其包含在我的设计中、但通过查看 PCB 布局、我可以对其焊盘高度进行不同的测量。

使用较高容差边界:

F11=F3=4.56

F3=4*F4+3*F5=4*0.7+3*0.67=4.81

4.81与4.56完全不同

然而、使用较低的容差边界:

F11=F3=4.46

F3=4*F4+3*F5=4*0.65+3*0.62=4.46此测量值匹配。

我很困惑、我是否应该计算这两者之间的平均值?

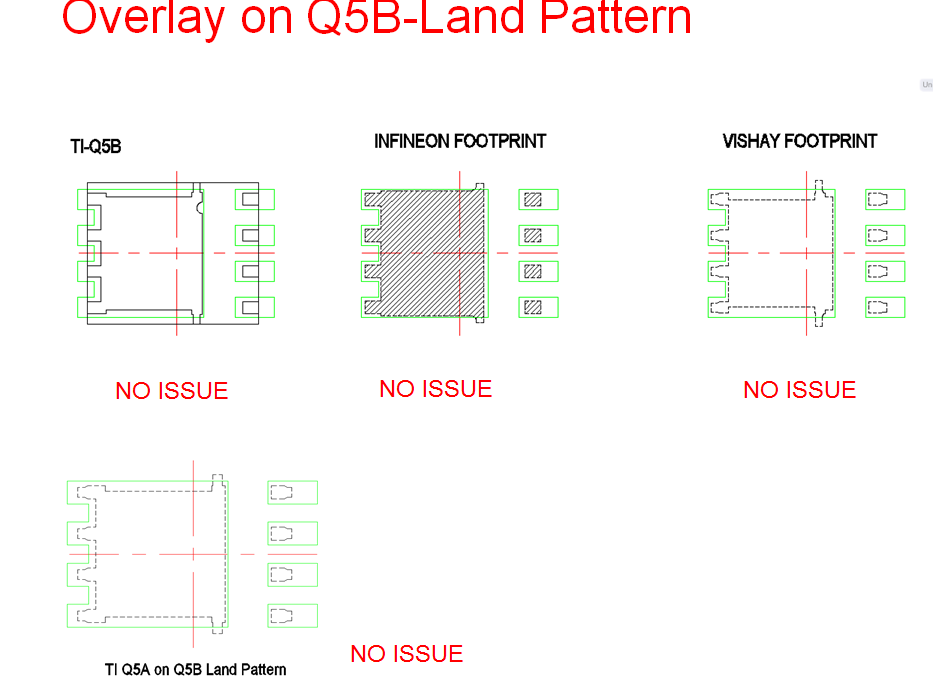

我还尝试调整此封装、以便可以在 相同封装上对 BSC117N08NS5ATMA1等备用使用 PG-TDSON-8

提前感谢。