LDO 专家、您好!

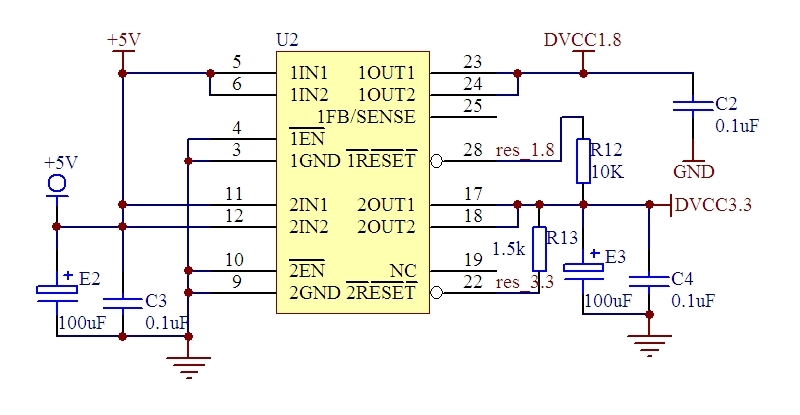

我遇到有关 TPS767D318的问题、您可以看到以下原理图、客户犯了错误-将 res1.8V 连接到 DVCC_3.3。

客户知道这不是正确的设计、他们将在下一版本设计中进行修改。

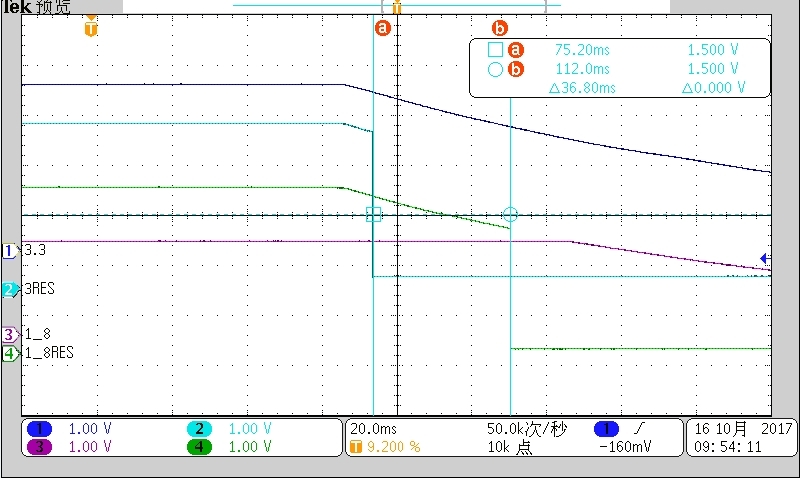

但基于此设计、我们找到了有关 res_1.8的有趣测试结果、您可以找到如下所示的测试波形。

测试条件:

当 VIN 5V 开始断电时、监测 DVCC3.3和 Res_3.3以及 DVCC1.8和 Res_1.8。

从测试波形可以看出、DVCC3.3首先下降、当 DVCC3.3低于3.16V 时、res_3.3变为逻辑"低电平"。

此外、您还可以看到、在 DVCC1.8开始下降之前、res_1.8下降到 DVCC3.3 (这是有道理的、因为 res_1.8被上拉至 DVCC3.3)。

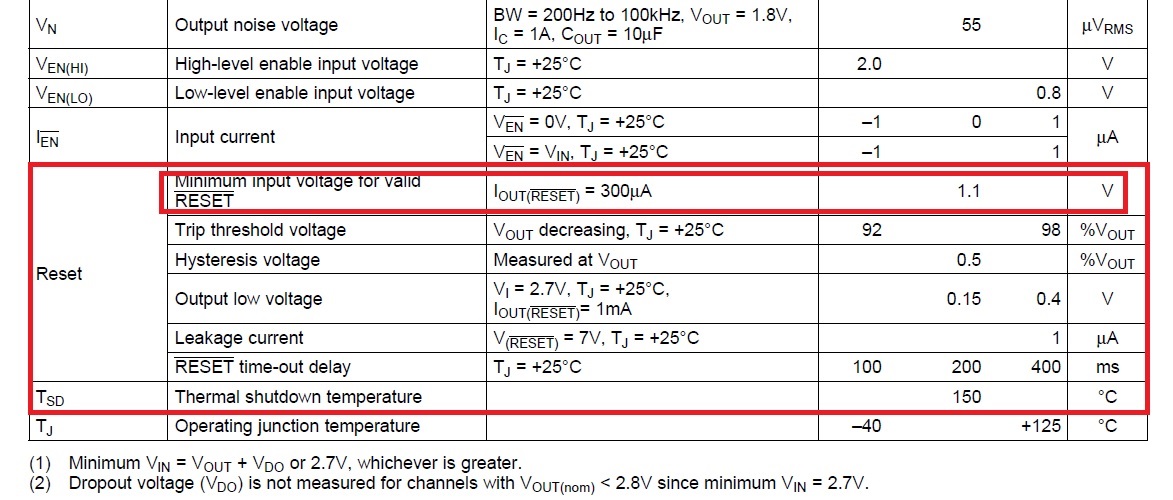

但是、您可以看到 res_1.8随后在 DVCC1.8开始下降之前变为逻辑"低电平"。 您能帮助您对此测试结果发表意见吗? 为什么?

此致

IVEN XU