请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS53353 TPS53353数据表中描述的引导电容器(R9)建议值为2Ω μ F。

①If μ V 噪声和振铃条件良好、引导电容器是否设置为0Ω μ F、没问题?

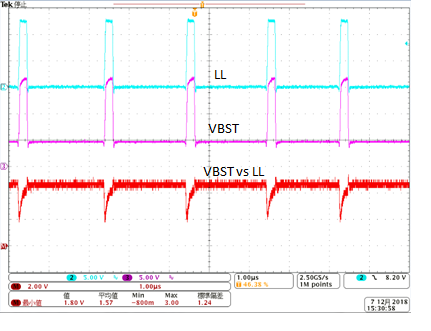

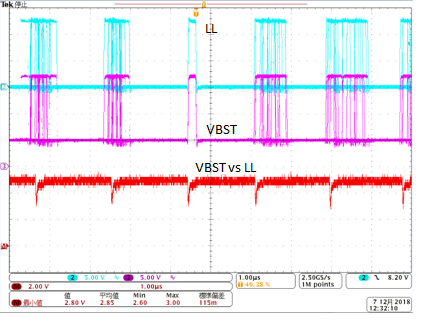

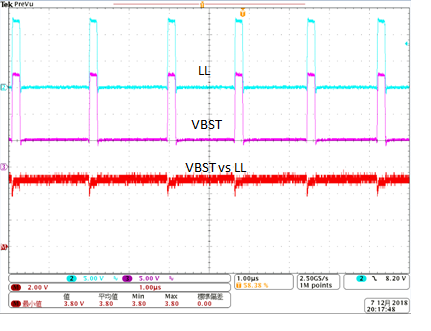

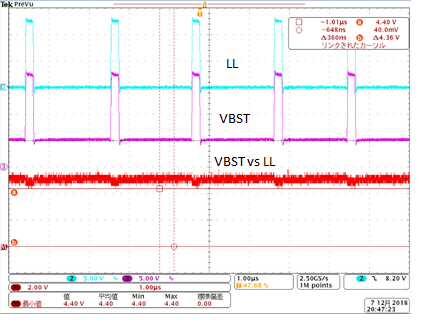

※下面连接了一个客户波形、大引导电容器将下降 VBST (相对于 LL)。

当更改为小于2.4Ω Ω 时、VBST 电压不会下降。

客户希望确认0Ω 条件为 OK 或 NG。 (当 NG 时、最小值是多少?)

・22Ω μ A

・5.6Ω μ A

・2.4Ω μ A

・0Ω μ A

②Additional 问题、数据表 P27说明"使用分离的过孔或迹线将 LL 节点连接到缓冲器、自举电容器和纹波注入电阻器。 请勿将这些连接组合在一起。"

当结合缓冲器和纹波注入电阻器时、是否有可能超过 VBST 压降?

请告诉我这些组合电路的影响。

此致、

Satoshi