主题中讨论的其他器件: TPS62826

您好!

由于组件短缺、我们重新设计了产品中的电源。 我们现在正在执行自动重启测试、其中产品断电并每2分钟重启一次、以进行验证。

我们注意到、在 TPS5432上、大约20%的 DUT 发生故障(测试批次30个单元)

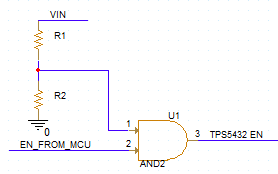

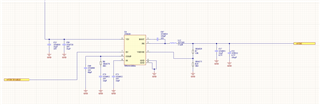

在该产品中、我们使用3个 TPS5432。 其中2个产生3.3V 电压、1个产生4V 电压、所有电压均来自相同的5V 电压。 故障始终是4V 转换器。

对故障进行去焊后、TPS5432均显示 PH 引脚和 GND 引脚之间的短路、测量值介于0.4和3.5欧姆之间。

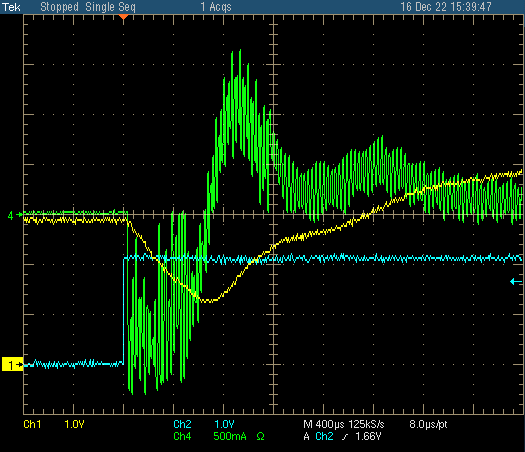

首先估算出、PH 引脚上可能会出现一个到高电压(尽管我们无法使用有源示波器探针测量此电压)。 作为测试、我们在测试批次中从 PH 引脚到+5V 输入添加了一个二极管。 这没有解决我们的问题,问题仍然存在。

左侧的转换器是4V 转换器、右侧的转换器是3.3V 转换器

显然、转换器不需要处理温度问题或负载过重。

是否有任何关于导致设备故障的原因的想法?

谢谢!