主题中讨论的其他器件: TPS3710

您好!

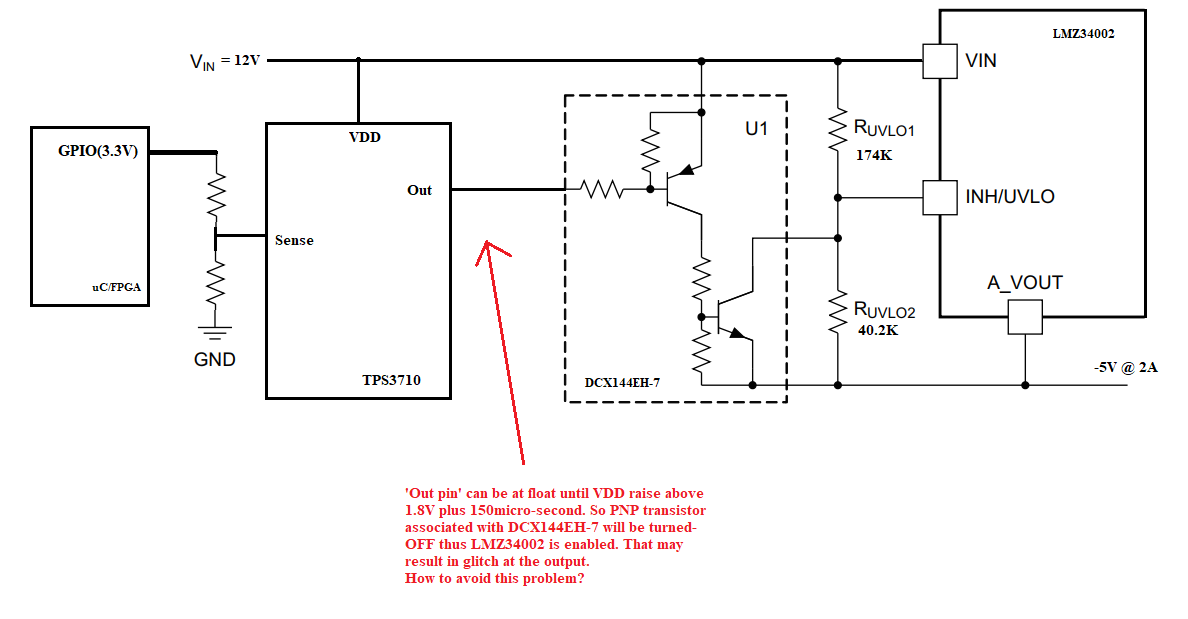

LMZ34002用于从12V 输入电源生成-5V@1.6A。开关频率选为500kHz、 10ms 软启动和 UVLO=6.5V。

根据项目要求、LMZ34002应在输出被禁用的情况下加电。 页面:21上的原理图与我们的要求完全相反。

从数据表中可以很好地了解到 INH/UVLO 引脚无法直接驱动、因此必须使用一些电平转换机制。

在这里、必须从 UC/FPGA 的 GPIO (间接)控制 INH/UVLO 引脚。

我无法确保该 GPIO 在初始上电期间或复位期间接地、它在初始上电期间或复位期间处于高阻抗状态。

但在 UC/FPGA 的 GPIO 驱动为高电平(3.3V)之前、LMZ34002输出应保持禁用状态。 那么、只有我们才能实现正确的加电排序。

问题1. 请建议一种实施上述要求的机制?

请找到随附的图像、该图像使用 DCX144EH-7和 TPS3710满足上述要求。

但由于以下原因、它可能会在上电期间在输出端产生干扰。

TPS3710的 OUT 引脚处于未定状态、直到 VDD 斜升至1.8V 以上加上150micro 秒延迟。 因此、它可以关闭与 DCX144Eh-7关联的 PNP 晶体管、从而开启 LMZ34002。

问题2. 此问题是否会在初始上电期间导致输出干扰? 如何解决此问题?请查看所附图片

提前感谢

Deepak V