请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS544C20 您好!

我对 TPS544C20 EVM 有疑问。

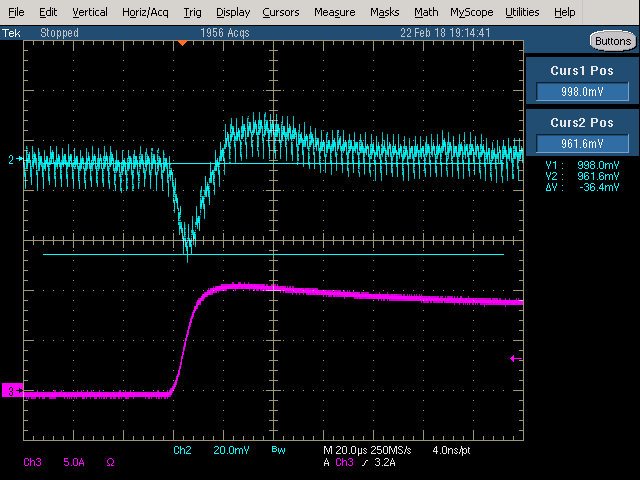

我在 EVM 上测量了0A 至10A 瞬态的瞬态响应

然后、我可以看到大约35mV 的压降、如下图所示。

我在 VOUT 上添加了10个100uF 的电容(TP11-TP7为5个、C18/19/2/25附近为5个)、以减少压降。

但压降波形 根本没有改善。 我可以看到几乎相同的波形。

您是否了解了为什么使用额外的电容(100uF x 10pcs)根本没有改善压降?

此致、

OBA