主题中讨论的其他器件: UCD3138、 ISO7831

大家好、

客户正在使用 LMG3410-HB-EVM 在 LLC 对其多种产品进行测试。

目前、移除了 EVM 上的两个 SN6505、次级侧的3.3V 电压为 ISO7831和 UCD3138的引脚1供电;初级侧的 GaN VDD 由12V 辅助电源提供。

根据用户手册、U3、U4和 R2已移除、R1、R18和 D1已添加。

发现一旦低侧栅极被切换、U2故障引脚信号将被拉低、导致高侧栅极无法工作、并且没有12V 输出。

但是、如果将 SN6505用作隔离式电源、则不会出现上述问题。

确认 Vdd 12V 和3.3V 稳定、并首先排除 UVLO 问题。 OCP 可以导致它吗?

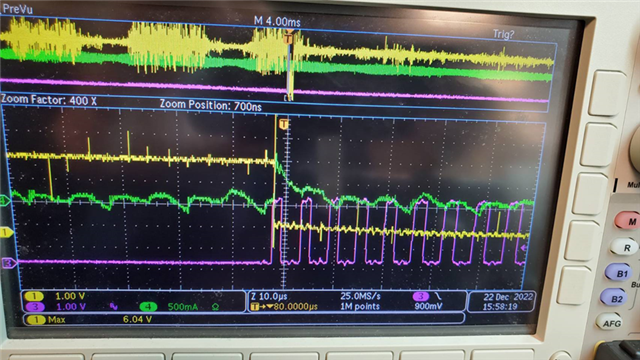

您可以参考以下波形

CH1:U2引脚5

CH3:UCD3138的 U2引脚4低侧

CH4:低侧栅极电流

CH1:U2引脚5

CH3:UCD3138的 U2引脚4低侧

您可以看到、当栅极开始开关时、故障下拉为低电平