主题中讨论的其他器件:CSD18543Q3A、 CSD19533Q5A、

大家好、

我有一个基于 LM5117的100W 48V 至14V 降压转换器。 我将 CSD19533Q5A 用于同步 FET、将 CSD18543Q3A 用于控制 FET。 由于库存原因、我还将 Infineon BSZ099N06LS5ATMA1用于控制 FET。 下面是原理图的快照:

-输入和输出端有更多的电容(在所示区域之外)

电感为33uH

上面的原理图中显示的组件也在这里的布局中:

这正是我所要努力的:

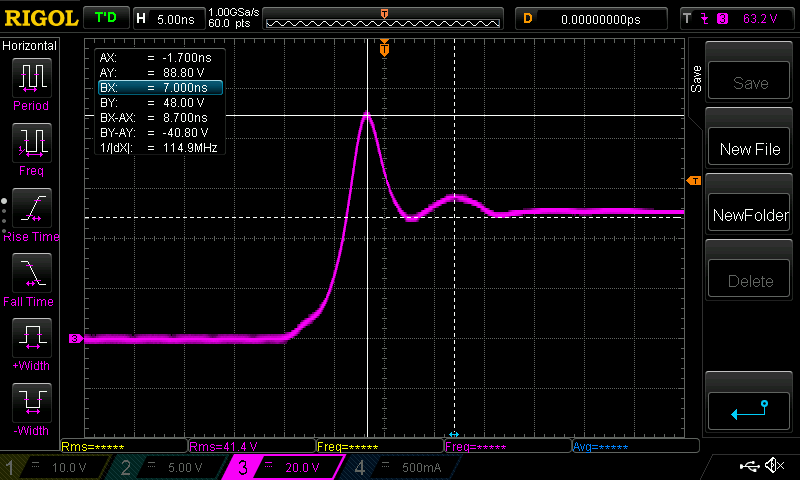

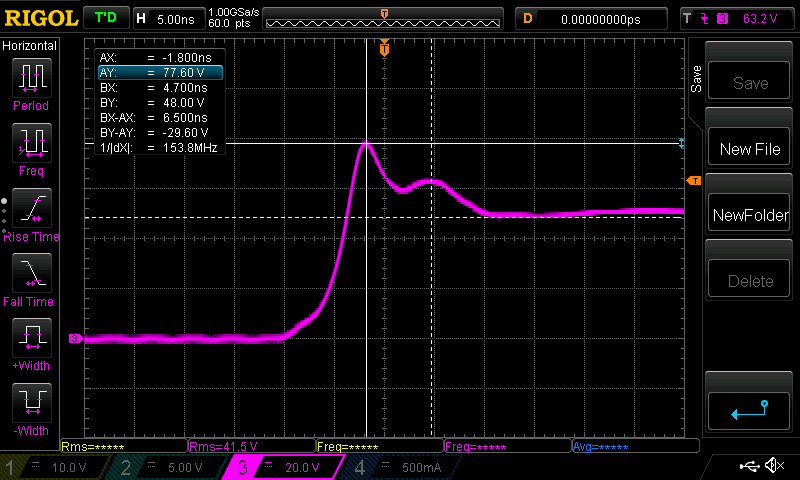

1、一开始没有缓冲器(R2、C6保持断开)、看到预期的振铃

2.为缓冲器使用了一个1500pF 电容器和一个5.6欧姆电阻器。 SYNC FET 的 C_OSS 处于350pF 至500pF 范围内。 我想我会放一些阻尼、稍后再对其进行调优。 但是、

1500pF 电容器根本没有改变振荡的频率--实际上只减少了一点! 当然、振幅减小了一点、振铃更快地结束。 但频率没有显著变化。

4.振荡振铃/振幅的峰值在满负载时上升到100伏、这意味着该缓冲器不会工作

5.尝试增大电容(1800p、2200p),但我看到频率或振幅没有变化

6、最终我将另一个电阻焊接到顶部、得到了可接受的裕度、从而将电阻减半。 下面的一些波形:

我相信,应该可以有一个更好的缓冲器--但如何做到这一点? 如何使用所有寄生效应对该电路进行建模、从而解释观察结果?

谢谢!

S