主题中讨论的其他器件: UCC24636

您好!

我目前正在调试 UCC28740 + UCC24636的原型。

5V - 2、5A

在变压器一次侧(极化错误)周围进行了明显的校正后、我获得不稳定的5V 输出。 并且电路不能承载任何负载。

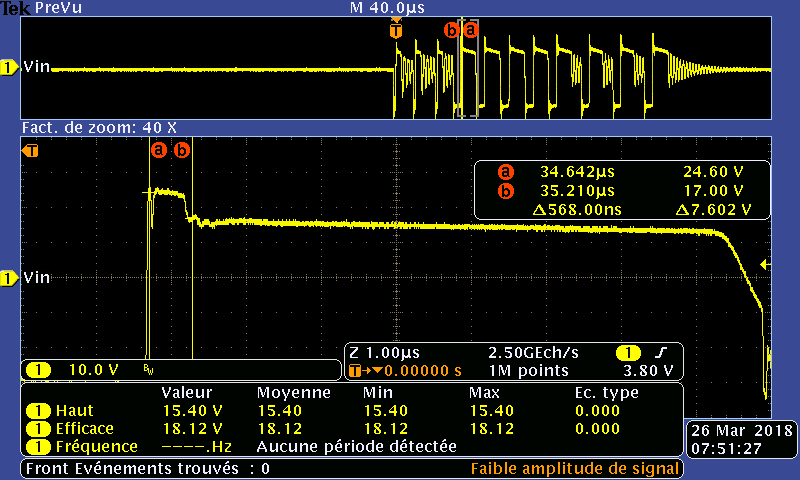

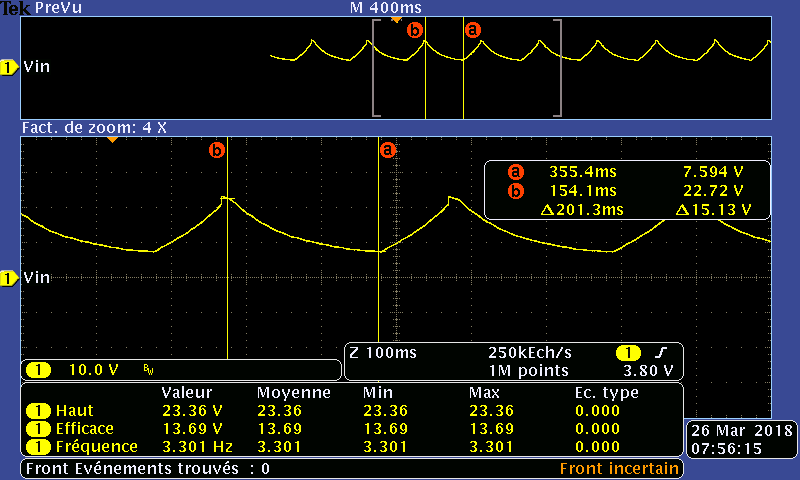

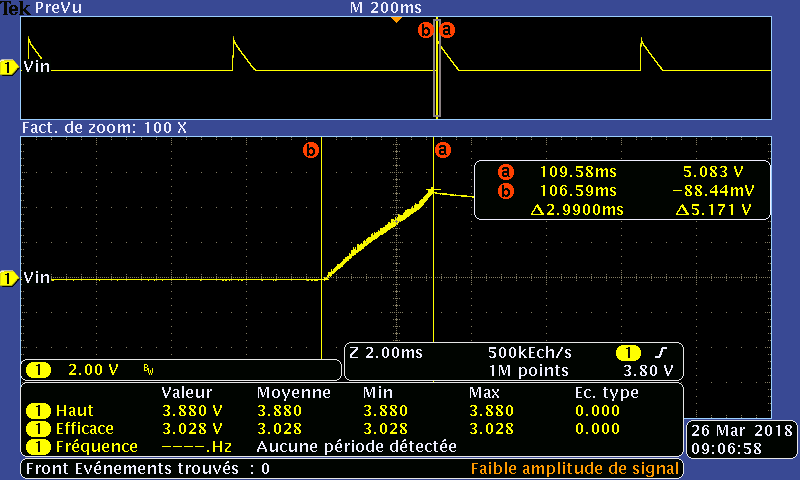

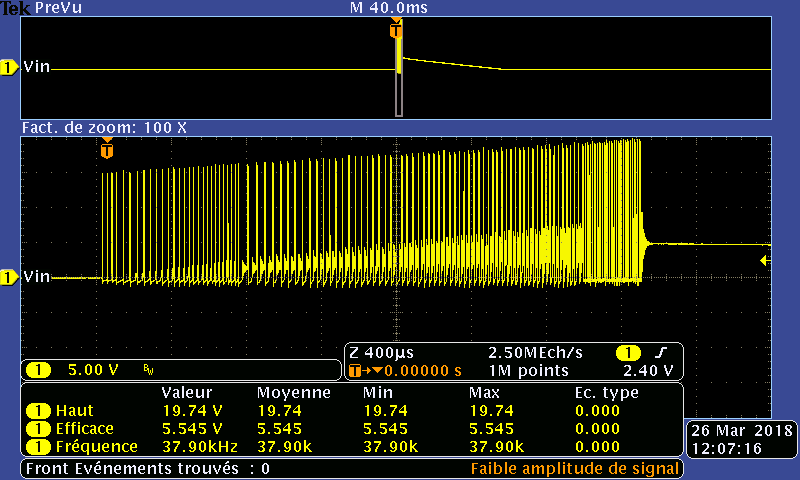

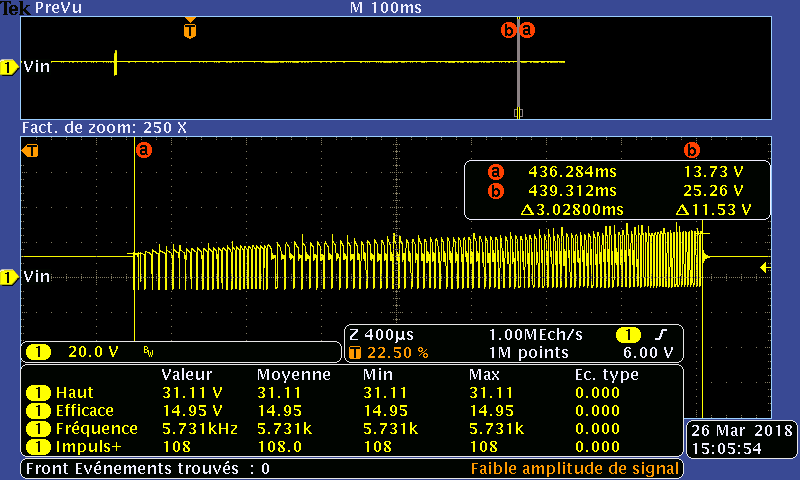

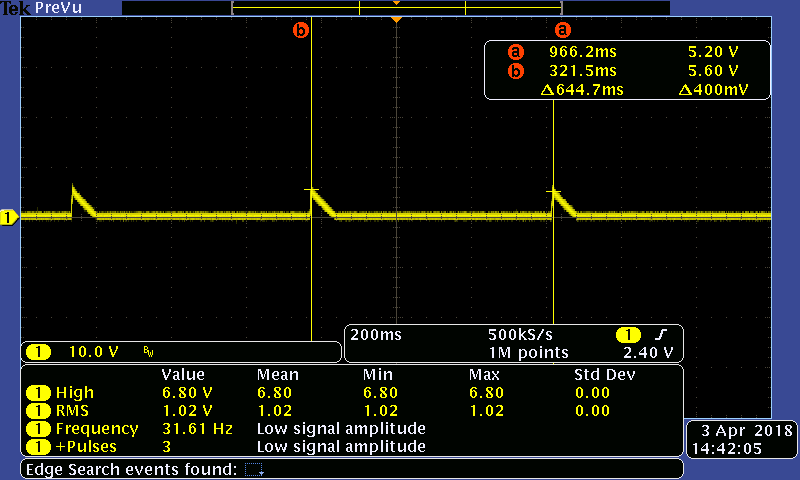

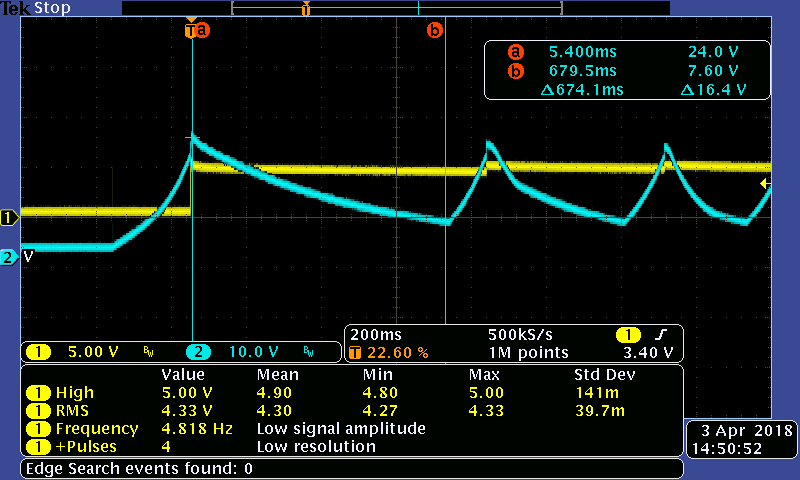

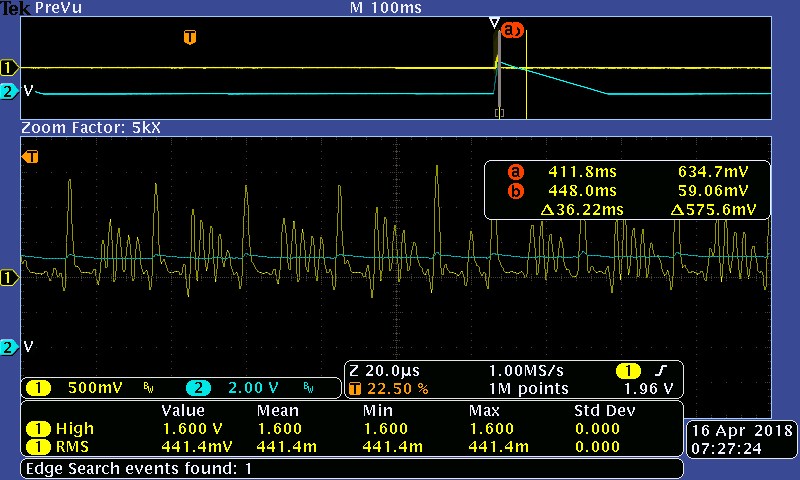

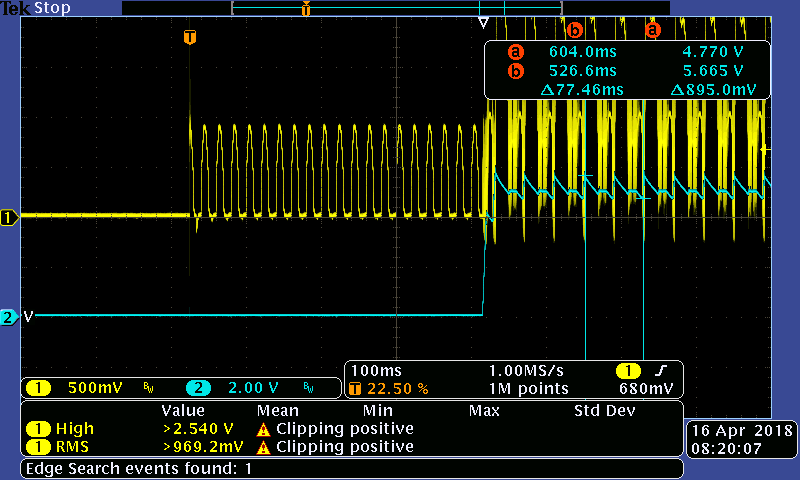

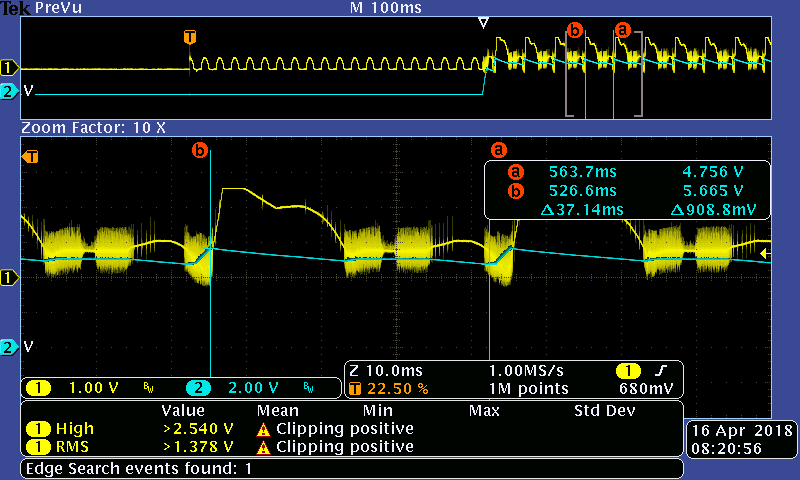

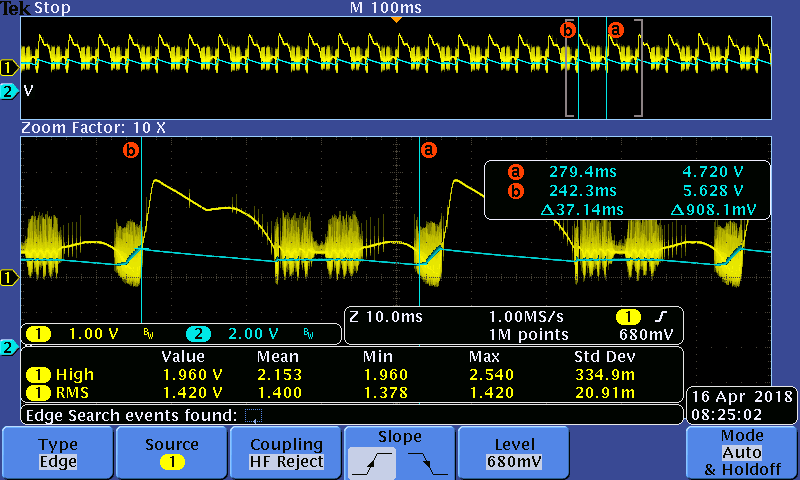

UCC28740似乎在少数开关上正常工作、可获得5V 电压、但会受到默认设置的影响并关闭。

我们可以看到 VDD 降至 UVLO 7V 以下

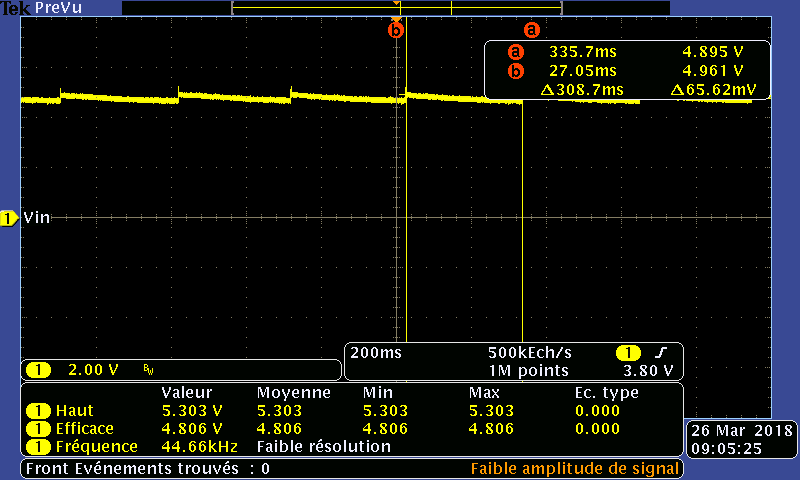

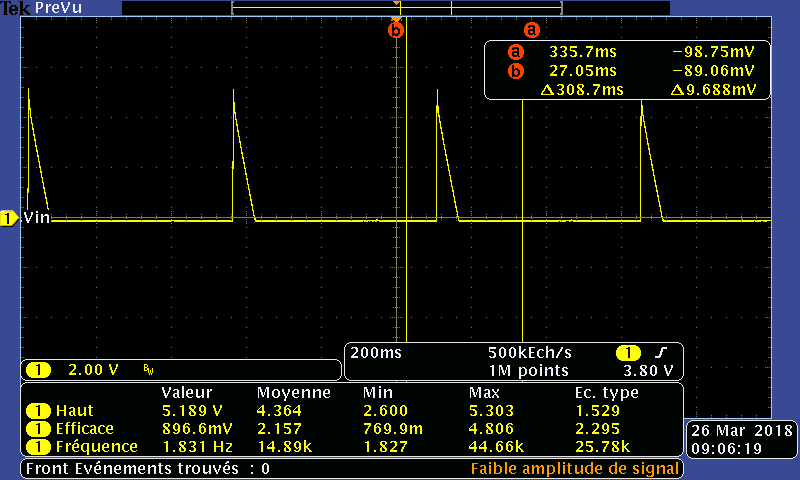

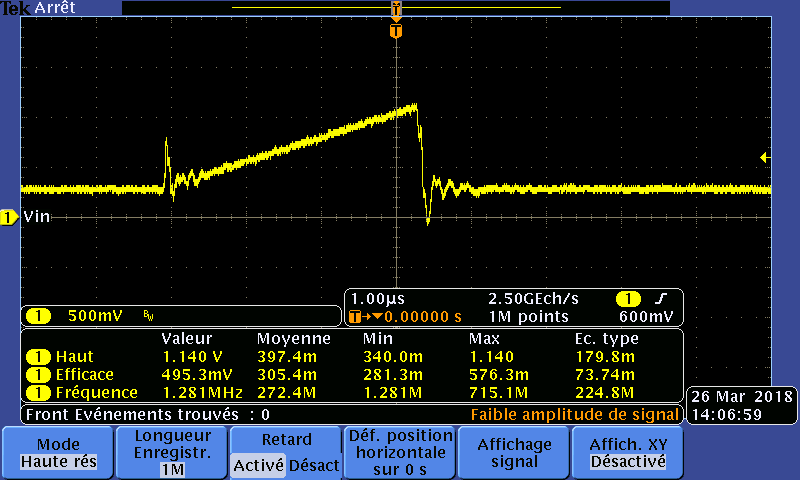

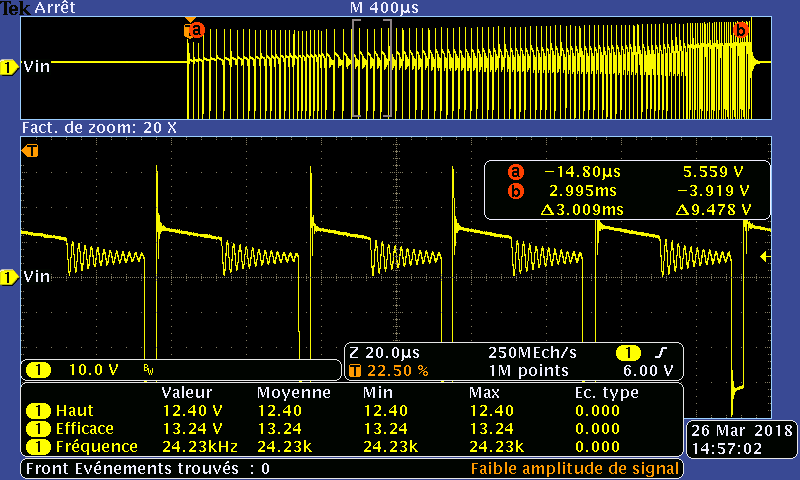

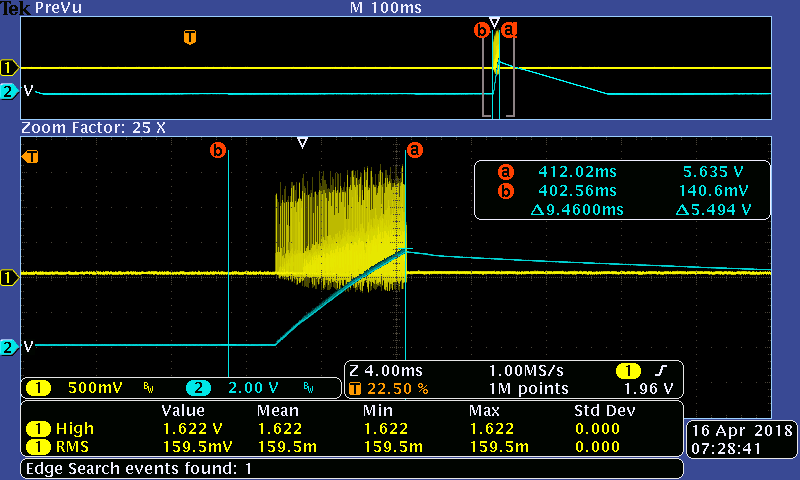

我开始使用2个差分探头进行进一步调查、但我烧毁了第二个 PCB (RCS 电阻器)。 (在第一个 PCB Rls 上、RCS 和 UCC28740被烧断)

我在初级 GND 和 VDD 之间使用了一个差分探针、在初级 GND 和 DRV 之间使用了第二个差分探针。

DRV 上的探针能否触发 MOSFET 并在 RCS 电阻器上构建短路?

在我继续进行现场测试尝试之前、您能否对原理图进行完整性检查?

谢谢你

e2e.ti.com/.../Power_5F00_SCH_5F00_UCC28740_5F00_01.pdf

此致、

Frans