请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS24710 您好!

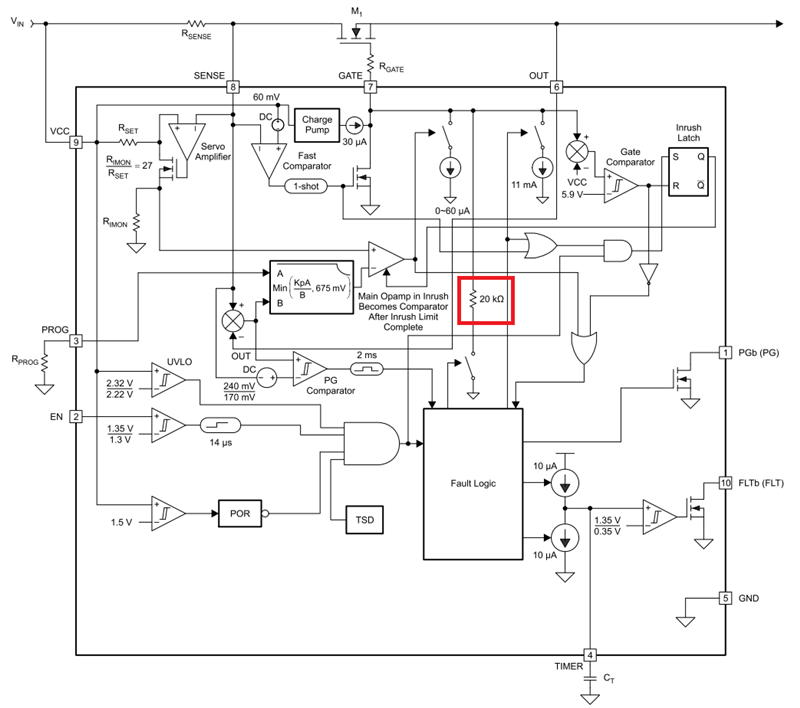

TPS24710数据表的第14页提到、如果芯片芯片温度超过 OTSD 上升阈值、栅极引脚将由内部20kΩ Ω 电阻器放电至 GND。

因此,在将 EN 引脚拉至低电平时,栅极引脚是否也通过内部20kΩ Ω 电阻放电?

如果是,在将 EN 引脚拉至低电平时,是否可以通过外部分压电阻器(低阻抗)向栅极引脚施加偏置电压(1V ~ 1.5V)?

此致、

加藤