请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS7A8101 大家好、

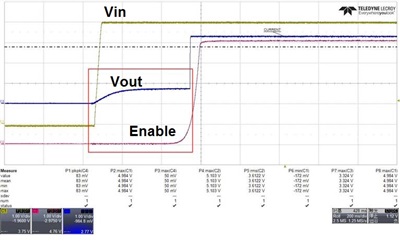

我的客户正在评估我们的 TPS7A8101。 下面是 启动(VIN、Vout、使能)波形、也显示如下:

此问题描述如下:

当 Vin=5V 时(显示在波形中、黄色曲线)、延迟大约500ms 后、将使能引脚拉高(粉色曲线)、但在使能引脚变为高电平之前、这些引脚为 Vout=0.7V、但不是大约0V。 这将导致客户使用问题。

那么、为什么 TPS7A8101在启用器件之前具有输出? 是否有 解决方案来避免此问题? 谢谢。

此致、

Sulyn