主题中讨论的其他器件:TLV62568

您好!

我需要调整 Sky FEM 的 PA 输出。 遗憾的是、这只能通过调节该芯片的 VCC-TX 来实现、而没有机会通过 PA_IN 甚至 VPC 来实现(我与 Sky 就该芯片进行了长时间的对话)。

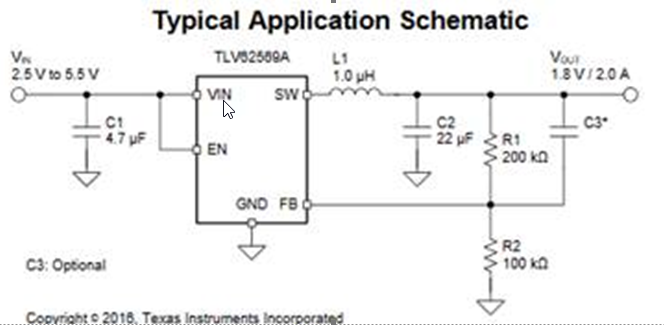

此芯片当前(其在生产中的给定设计)的源电压为3.3V -这对于最大 PA 输出是必要的。 为了实现更低的输出、我需要降低 VCC_TX、例如在1.5V 至3.3V 之间进行4步。我的计划是使用焊接桥接并联电阻器在特定值之间改变 R2。

现在、3.3V 是主电源电压:我无法承受降压转换器产生的任何压降电压。

问题:该芯片是否能够在不产生压降损耗的情况下将 VIN 传递到 VOUT?

或者、如果不是、在"全 PA"情况下、我能否通过额外的焊接桥接 VIN 和 VOUT 而不损坏任何东西?

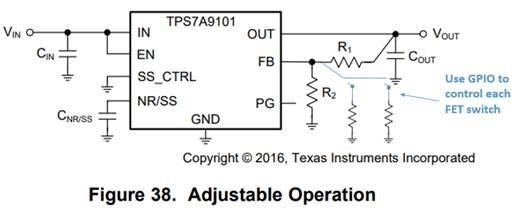

同样的问题是、如果我使用此设计(会考虑它-无线圈、无 EMI -但在这里、我知道存在0.2V 电压损耗):

谢谢!