大家好、

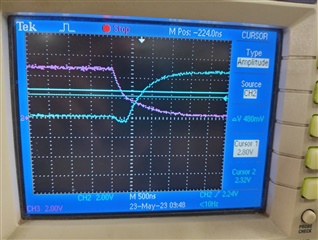

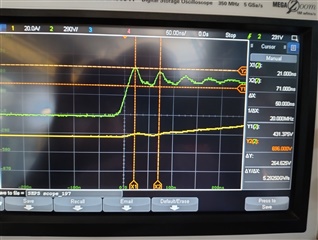

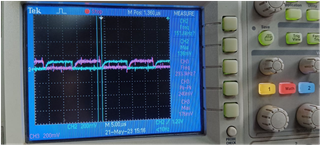

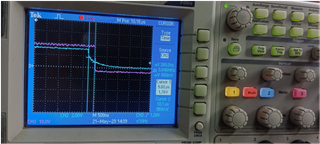

我正在将 UCC21710-Q1驱动器 IC 用于 SiC MOSFET (C3M0040120D)。 使用 DSP 板通过160ns 死区时间生成50kHz 信号。 下面给出了 DSP 卡的输出、死区时间为160ns。

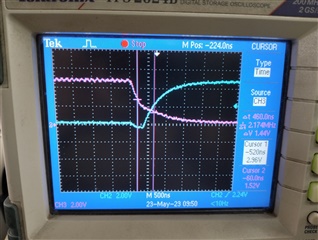

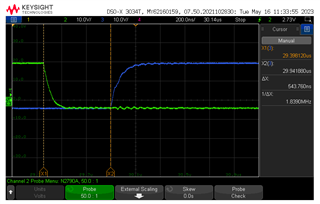

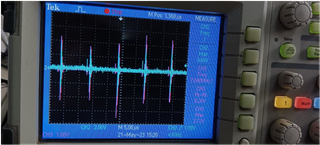

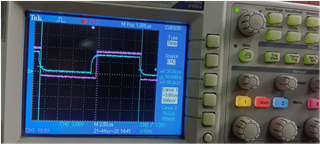

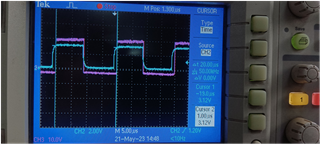

相同的信号通过 FRC 电缆提供给驱动器板的输入、驱动器的输出如下所示

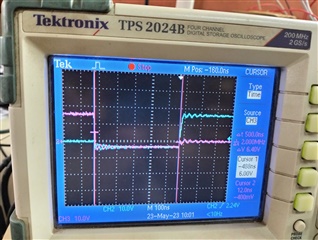

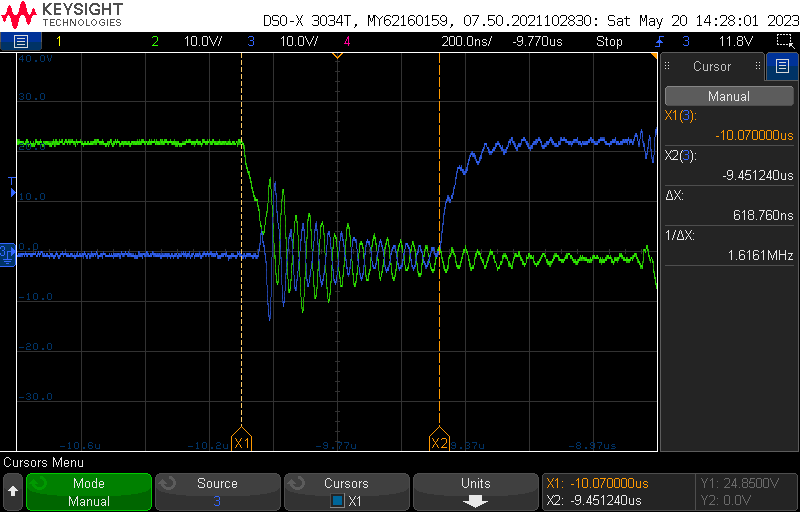

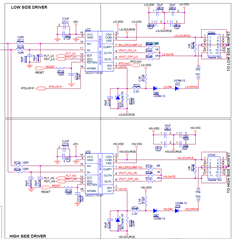

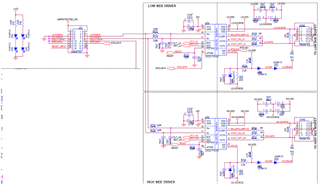

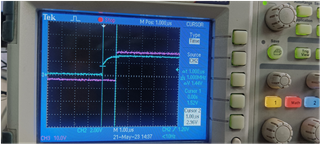

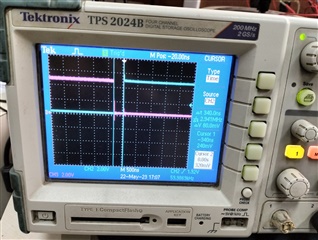

我已经观察到死区时间差为350ns。 您能不能建议、为什么要在栅极脉冲中增加额外的死区时间。 我已根据数据表在驱动器 IC 的输入端添加了 RC (R=120R、C=56pF)滤波器。 下面提供了驱动器电路以供您参考

提前感谢您的意见。

此致

Umamaheswararao.

死区时间为340ns 的输入脉冲

死区时间为340ns 的输入脉冲  死区时间为440ns 的输出脉冲

死区时间为440ns 的输出脉冲