在我的电路中、从 BP 到自举二极管很容易损坏。 当电路发生故障时、 BOOT 不再充电、但 BP 引脚上仍有~6.5V 电压。 在正常工作的 TPS40305上 、我测量从 BP 引脚到 BOOT 引脚的0.68V 二极管正向电压。 在发生故障的 TPS40305中 、该电压变为0.18V。 自举二极管是否可能损坏?

Webench 用于设计在电流为5A 时具有20V 至12V 电压的电路。 15V 输入和20V 输入也使用了同一电路。 我意识到20V 处于器件限值、但我也看到了 当输入电压为15V 时 TPS40305启动故障。

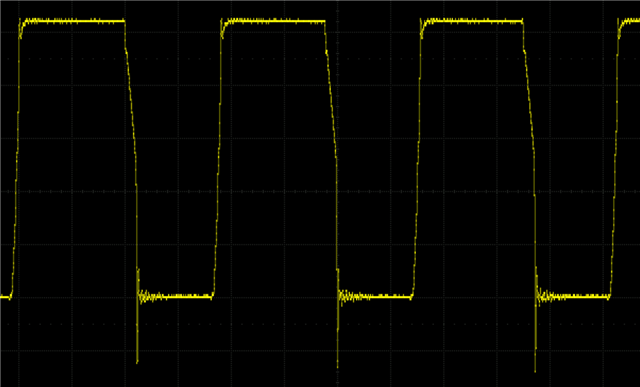

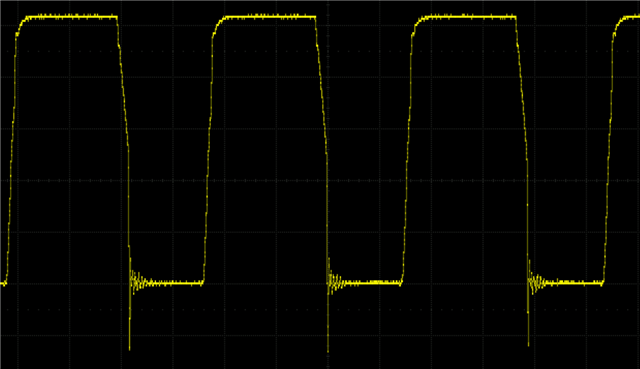

我看了看 SW 节点振铃。 我尝试在 BOOT 引脚和升压电容器之间连接一个2.2欧姆的电阻器。 在上升沿之后的振铃有所改善、但下降沿之后的振铃仍然很大。 请参阅添加该2.2欧姆电阻器前后的图:

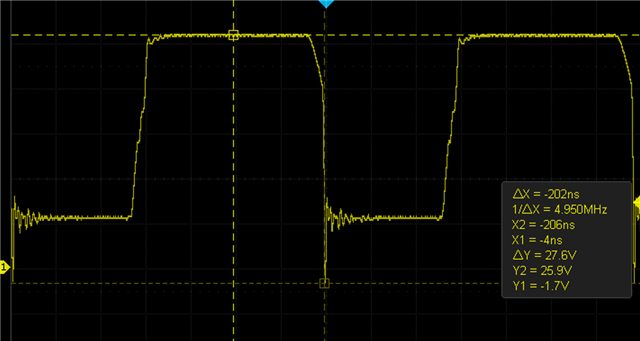

SW 节点上的电平降到-5V 的绝对最大额定值以下。 在 BOOT 引脚上、I 测量低于-0.3V 绝对最大额定值的电平:

这是否是造成损坏的可能原因? 或者是否存在其他原因? 为了使电路可靠、建议的下一步是什么?

谢谢!