器件型号:BQ76952

主题中讨论的其他器件:BQSTUDIO

配置这些多功能引脚时需要考虑哪些因素?

电源培训小程序码

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

DCHG 和 DDSG 引脚是多功能引脚、可配置为输出、用于在存在故障情况以及当前 FET 驱动器状态时向主机 MCU 发送信号。

通常、DCHG 和 DDSG 引脚将遵循 CHG 和 DSG FET 驱动器状态。 默认情况下、DCHG 和 DDSG 配置为 高电平有效 ,即,如果 CHG 或 DSG 为逻辑高电平(1),则 DCHG 和 DDSG 将为逻辑低电平(0)。

这些引脚还可以配置不同的输出、如下所示: 高电平有效 , 低电平有效 , 三态 , 弱下拉至 VSS , 弱上拉至 REG18 和 针对 REG18的高驱动 或 REG1 设置 PMBus 信号。

将引脚配置为 低电平有效、 然后、当 CHG 或 DSG 为逻辑高电平(1)时、DDSG 和 DCHG 状态将跟随状态为逻辑高电平(1)。 这仅在引脚配置为通过将 引脚 FXN1 和 引脚_ FXN0 引脚配置字段说明选择合适的位。

在以下示例中、我们演示了 低电平有效 行为、方法是配置 DDSG 引脚。

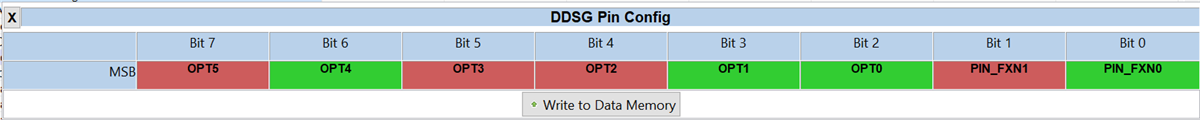

DDSG Pin Config 寄存器字段说明

位7 - OPT5:

注意:极性仅在引脚配置为 DDSG 模式时有效(在 GPO 模式中不起作用)

位6 - OPT4:位未使用

位5 - OPT3:

位4 - OPT2:

注意:当 OPT3设置为逻辑高电平时不可用(1)

位3 - OPT1:

注意:当 OPT3设置为逻辑高电平时不可用(1)

位2 - OPT0:

位1–PIN_FXN1和位0–PIN_FIXN0:使用两种引脚状态来配置引脚

注意:请确保为所需的引脚行为选择正确的引脚选项。

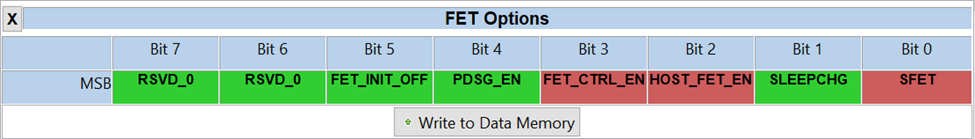

在正常运行期间、可以手动或自主控制 FET。 然而、只有在两种情况下才能启动 FET 控制、方法是先将 FET_EN 位的时间以及当 FET_CTRL_EN 已置位。 这可以在中找到 寄存器 中 BQStudio 的选项卡 设置:制造:制造业状态初始化[FET_EN] 和 设置:FET:FET 选项[FET_CTRL_EN] 和-90度。

或者、有关该寄存器的更多信息、可参阅器件技术参考手册(TRM) 表13-34. Mfg Status Init 寄存器字段说明 。

重要说明:

为了确保在使用 DDSG 和 DCHG 引脚驱动低侧 FET 时具有最快的关断时间、必须按以下方式设置以下寄存器:

在 设置:Protection:CHG FET Protections A 我们建议将该寄存器设置为0x18或0x98

在 设置:Protection:DSG FET Protections A 我们建议将此寄存器设置为0xE4

也可以使用 数据存储器 选项卡中、或通过将值写入 RAM 地址来实现。

将这些保护设置配置为上面指定的值以外的任何值都可能导致关断时间延迟一段未指定的时间、但在 NORMAL 模式下最多可能延迟250ms、在 SLEEP 模式下最多延迟1秒。