您好!

像许多其他海报一样、我对 TPS65130的负输出有问题。 我需要+/-15V 输出、电流大约为50mA、输入电压为+5.5V。 我将稳定的+15V 输出和-16.4V 输出、偶尔会出现瞬变(每秒左右)、并且会低至-26V。

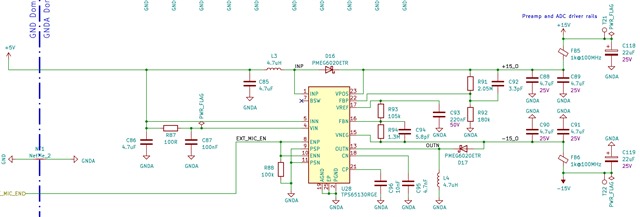

我的原理图如下所示:

我已阅读过许多类似的帖子、通常建议添加~50k 与 C94串联。 遗憾的是、这不会改变我的电路的行为。

VREF 上的电压为1.2V

FBP 的电压为1.213V

FBN 处的电压约为-0.32V、并且不稳定。

我已经购买了 EVM 板并逐步对其进行了修改、直到它与我的板相同。 很遗憾、我无法重现故障-我在 EVM 板上得到+/- 15V、即使我移除了一些输出电容器(是的、我知道每个输出可能应该再增加几个电容器)。 我更换了电感器、二极管、禁用了省电模式、并且在反馈网络中具有完全相同的电阻器。 我相信 EVM 板现在具有与我正在开发的板完全相同的原理图、除非我漏掉了一些内容。

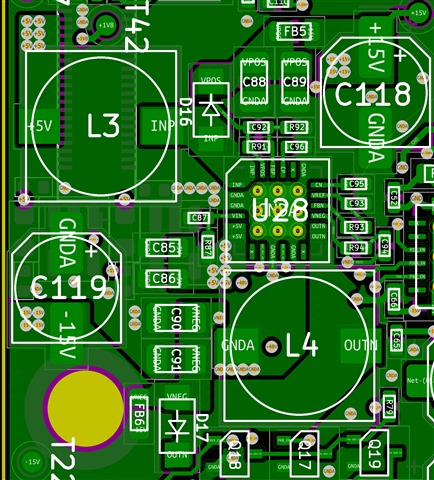

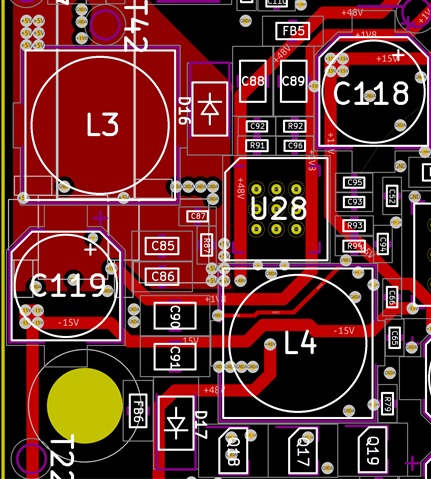

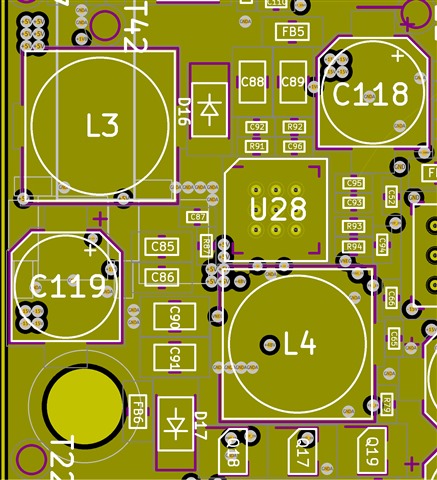

这就引出了布局-可能那里有什么问题。 布局如下:

我可以更改布局、使其尽可能类似于 EVM 并旋转一个新的电路板、但这是一个相当复杂的设计、因此我不想在没有证据表明它肯定会起作用的情况下冒险。

编辑:添加范围跟踪

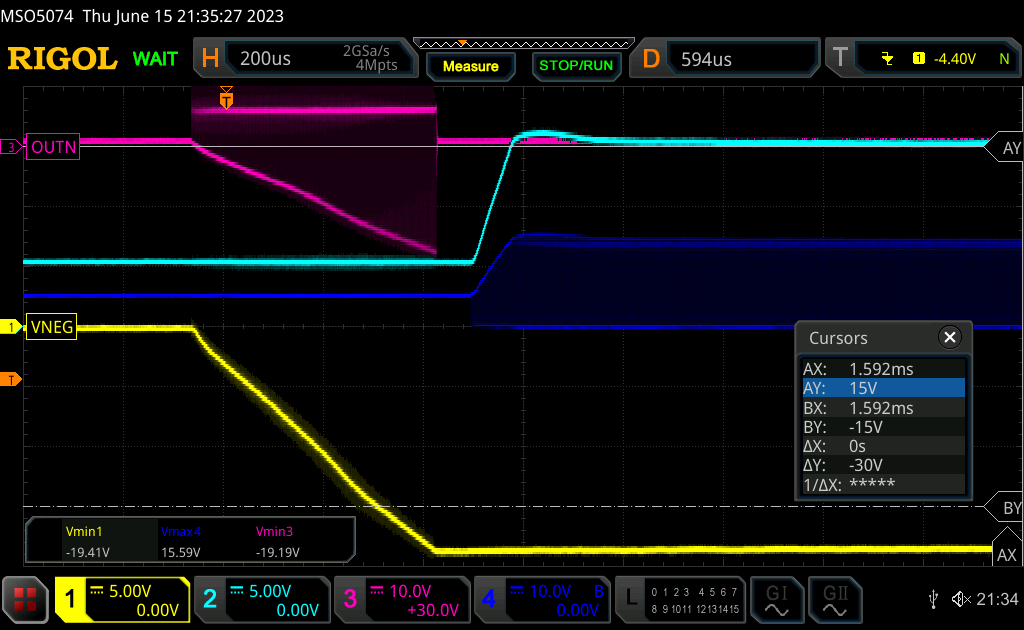

这里是启动。 您可以在通道1和2上看到 VNEG 和 VPOS。 VPOS 启动正常-它以一个小幅过冲达到+15V (光标 AY)。 VNEG 下冲-15V (光标所示)剧烈地降低至-20V 左右、并非常缓慢地开始恢复。

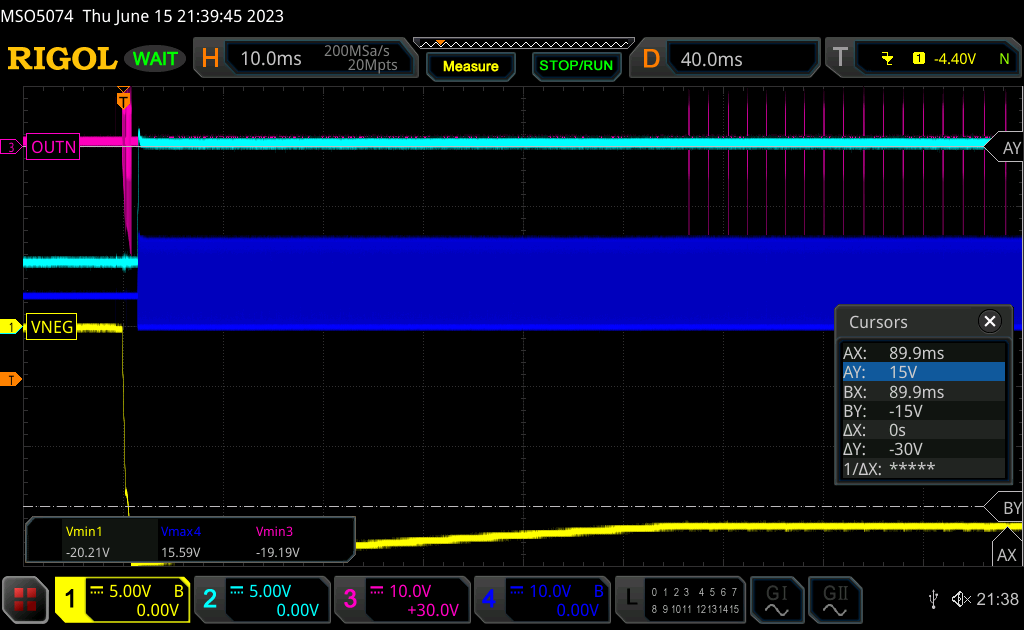

这里是相同的视图、具有更长的时基。 您可以看到 VNEG 在240ms 后稳定约-16.3V。 您可以看到、在此期间、OUTN (通道3)上没有开关事件、然后在240ms 后、开关以突发模式恢复。 这与持续开关的 INP (通道3)完全不同。 可疑。

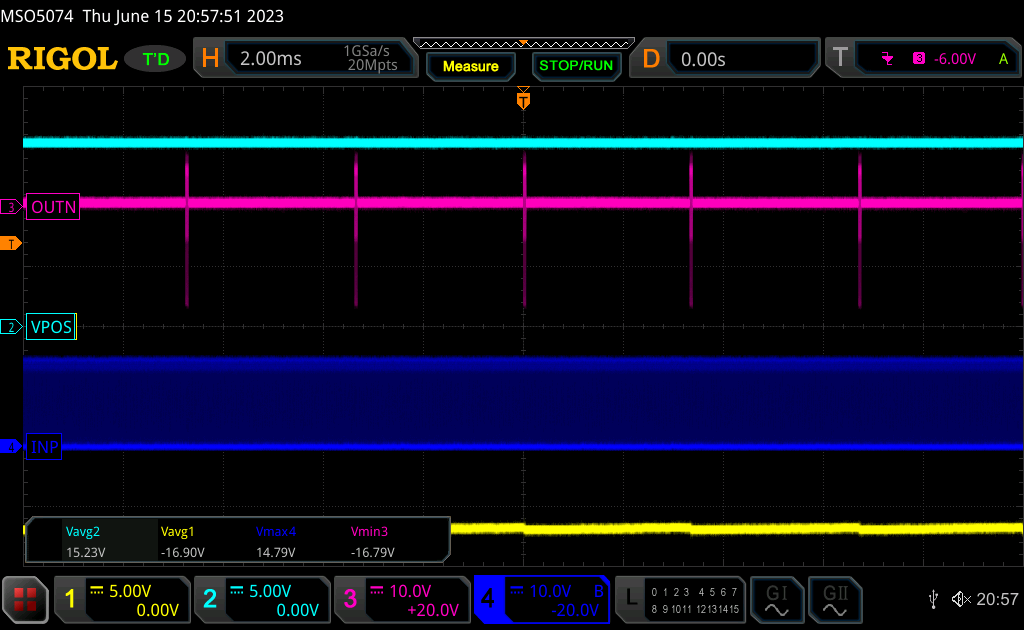

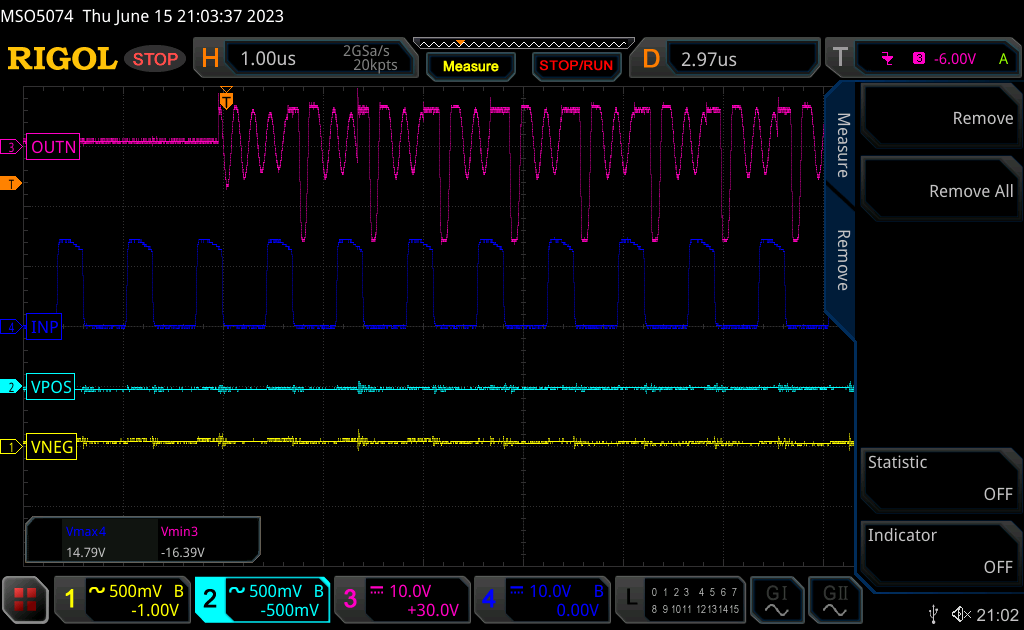

这是启动后的行为。 大家可以看到 VPOS=+15V、VNEG 大约为-16至-17V、并出现了一些频率渐升。 您可以看到 INP 不断开关、OUTN 在短时脉冲下开关。

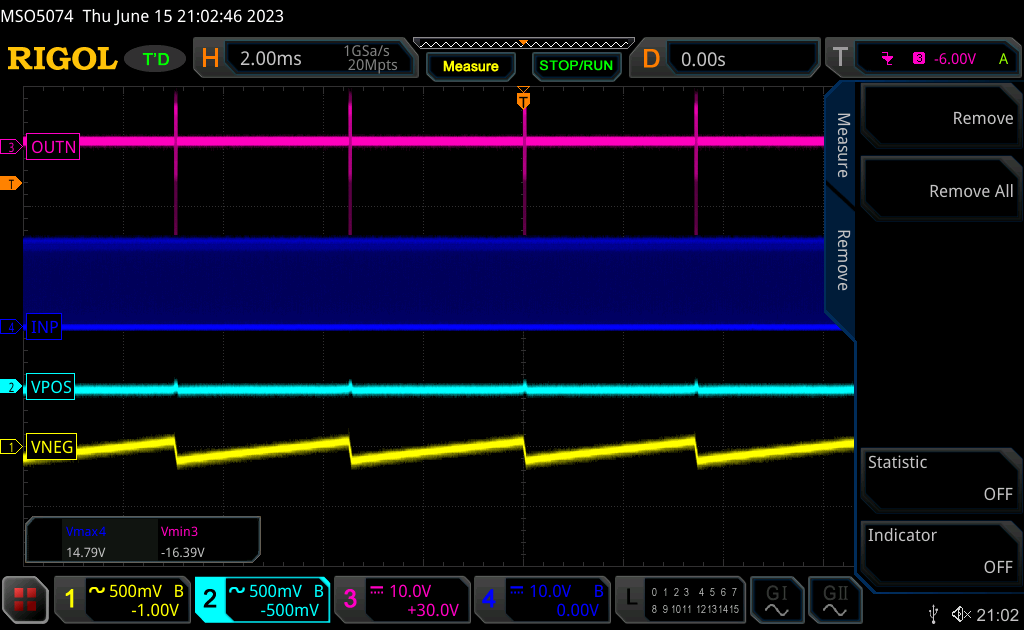

在这里、我使用交流耦合 VPOS 和 VNEG 放大斜坡。 平均值错误(约-16.4V)、斜坡的振幅约为0.3V

下面是一个较短的时基的视图、显示了 OUTN 上一个突发的开始。 INP 是一个很好的稳定方波、正如我所料。 对我来说,这是一件很奇怪的事情!

肯定这指向我的问题-为什么 OUTN 开关突发? 为什么信号振铃这么大? 我已经检查了 D17是否正确。 我还检查了 PSP 和 PSN 都为低电平、所以器件应该在两个电源轨上持续开关。

有什么建议吗?

谢谢。

杰夫