您好!

我的客户正在使用 TPS40345作为 FPGA 内核电源。

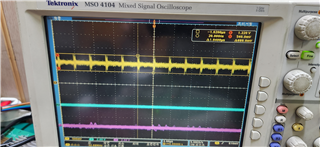

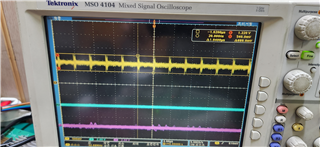

下面是输出纹波捕捉图像。 测得的输出纹波特性明显比数据表指导的差。

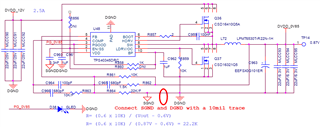

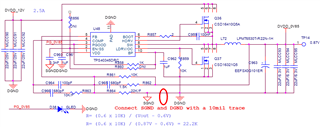

以下是客户设计文件和电感器数据表。

e2e.ti.com/.../LPMT6530_2D00_1H-Series-DataSheet_5F00_210219-_2800_1_2900_.pdf

Q1) 请查看 TPS40345的设计是否存在问题。

Q2) 请建议如何改善输出纹波特性。

谢谢你。

JH

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我的客户正在使用 TPS40345作为 FPGA 内核电源。

下面是输出纹波捕捉图像。 测得的输出纹波特性明显比数据表指导的差。

以下是客户设计文件和电感器数据表。

e2e.ti.com/.../LPMT6530_2D00_1H-Series-DataSheet_5F00_210219-_2800_1_2900_.pdf

Q1) 请查看 TPS40345的设计是否存在问题。

Q2) 请建议如何改善输出纹波特性。

谢谢你。

JH

Q1 ) 请查看 TPS40345的设计是否有问题。

不可以、TPS40345并不会在输出电压上产生极高频率(10s 至100s MHz)的噪声尖峰、这是正确的。

这些尖峰可能是真实的或示波器和探头的测量伪影、及其与 PCB 的连接。

Q2 ) 请告知如何改善输出纹波特性。

为了最大限度地减少示波器探头的噪声伪影:

将振荡器接地只连接至被测电路板上的1个接地点

使用"尖端和接地筒"方法并使用非常短的接地环路尽可能远离电感器(理想情况下在 PCB 的另一侧)测量 Vout

如果是真实噪声、则它可能在开关节点上振铃、耦合(或通过)电感器到输出电容器、然后由于电容器和布局 ESL 而不会在输出端消除。 从元件选型和元件布局来看、可能可以进行许多改进。

1) 1)改善开关节点处的振铃

现有布局的一项组件更改有助于减少开关节点振铃、因此其与 VOUT 的耦合是串联启动电阻器。 目前为2Ω μ A、可增加到4.7Ω μ A、以降低 SW 节点上的上升压摆率、从而降低振铃。

另一个元件是将其中一个输入和输出电容器替换为2.2-10nF 电容器、其自谐振频率与在开关节点上观察到的振铃频率匹配。 这将有助于降低这些高频下的输入和输出阻抗、同时允许电容器进行自阻尼。

此外、还可以对布局进行大量改进。

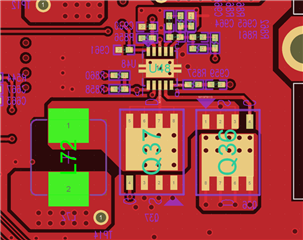

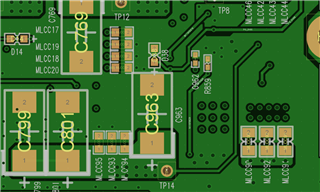

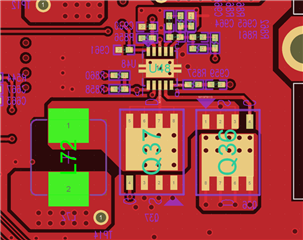

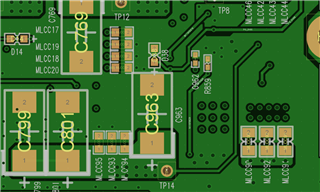

1) 当前布置在 PCB 背面高侧和低侧 FET 之间的反馈感应迹线可以绕过 MOSFET 的底部和右侧、以避免 MOSFET 之间的接地滑移以及增加高侧漏极到低侧的环路长度 源旁路

2)高侧漏极到低侧源极的旁路,目前在板的底部可以被拆分,将一半放在顶部,半放在底部,水平的方向,而不是垂直的。

3) 3)高侧 FET 上的漏极凸片过孔可以减小并重新分配、以允许底层上的接地覆铜填充在过孔之间

4) 4)可以在输出电容器的 GND 侧添加额外的过孔、以降低其电感回地

5) 5)应消除低侧 MOSFET 漏极选项卡中的过孔以及连接到 SW 节点的任何内部平面。

6) 6) 可以增加 SW 网络和 VOUT 网络之间的覆铜到覆铜间距、以减少从 SW 到 VOUT 节点的高频电容耦合

D7)在低侧和高侧 MOSFET 之间在 SW 和 VIN 之间添加 RC 缓冲器或高速整流器二极管、也有助于 降低开关节点的振铃能量、从而降低输出电压噪声。

8) 8)在 顶部的 VOUT 到同步整流器源极的 GND 之间添加小型2.2-10nF 0404电容器将有助于在高频噪声通过过孔之前消除该高频噪声