专家、您好!

是否存在某些可能导致 ACT 波从1变为0的可能性?

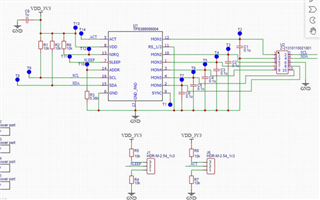

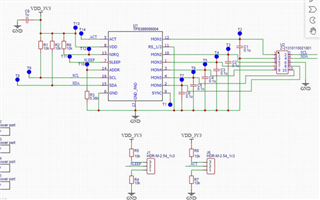

情况1:ACT 通过 R8上拉至 VVDD_3V3、如下图所示、ACT 在大约1.5ms 后变为0、然后返回1。

情况2:ACT 是直接上拉至 VDD_3V3。 ACT 不会变为低电平、但存在高噪声尖峰。

此致、

文廷

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

专家、您好!

是否存在某些可能导致 ACT 波从1变为0的可能性?

情况1:ACT 通过 R8上拉至 VVDD_3V3、如下图所示、ACT 在大约1.5ms 后变为0、然后返回1。

情况2:ACT 是直接上拉至 VDD_3V3。 ACT 不会变为低电平、但存在高噪声尖峰。

此致、

文廷

文婷您好!

原理图和上拉电阻器应该不会有问题。

有关详细信息、请参阅此帖子。

此致!

沃尔特

请注意、TDA4x PDN-3x v0.23 (或更高版本)框图已按如下方式更改了 TPS389006004-Q1 (安全电压监控器、也称为 SVS)上的 ACT 和 VDD 连接:

SVS VDD 电源连接需要从"常开"VCCA_3V3 (=VSYS_3V3)更改为"PMIC 控制"电源轨、以便通过 SVS 器件上电循环来复位置位已置位的 IRQn 信号。 在功能测试期间、发现如果 MCU 处理器与 SVS 器件的 I2C 通信丢失、则 SVS 有效的 IRQn 无法复位。 如果发生 MCU 电源错误(即 MCU 电源出现故障)、就会发生这种情况、因为这将导致 PMIC PFSM 将系统转换到所需的安全恢复状态(使所有 SoC 电源断电)。 但是、如果 SoC PDN 的输入电压(VSYS_3V3)保持通电、 然后、通电的 SVS 器件将保持置位的 IRQn、并且系统将无法执行 SoC 冷启动尝试、因为先前置位的 IRQn 将导致 PMIC 中止 SoC 上电序列尝试。 SVS 器件下电上电将复位置为有效的 IRQn 信号、从而启用所需的 SoC 冷启动尝试。 通过将"常开" VCCA_3V3电源连接替换为 PMIC 控制的电源轨(VDD_MCUIO_3V3源自 PMIC 的 LDO2 Vout)、SVS 器件在进入安全恢复状态时将发生下电上电事件(根据下表)。 如果主域电源发生故障、PMIC 将系统转换为仅 MCU 状态、从而允许 MCU I2C 通信评估并可能记录故障源。 如果需要系统冷启动尝试重新启动到完全激活状态、MCU 可以使用 I2C 通信清除置位的 IRQn、因为如果是由随机噪声事件或取决于温度、故障可能会清除。

SVS"运行"输入连接需要从连接到 PMIC 使能输入并连接到 SVS VDD 电源的"SOC_PWR_EN"更改为"ACTIVE"输入。 在 VSYS_3V3之后作为 SoC 上电定序的一部分启用新的 VDD_MCUIO_3V3电源连接。 此更改将避免在器件未通电时在 ACT 输入端驱动高逻辑信号。

PDN 状态:激活 仅 MCU 安全恢复

主电源=开启 主电源=关闭主电源 =关闭

MCU 电源=在 MCU 电源上=在 MCU 电源上=关闭

SVS-A =导通 SVS-A =打开 SVS-A =关闭

SVS-B =导通 SVS-B =打开 SVS-B =关闭