主题中讨论的其他器件: INA280

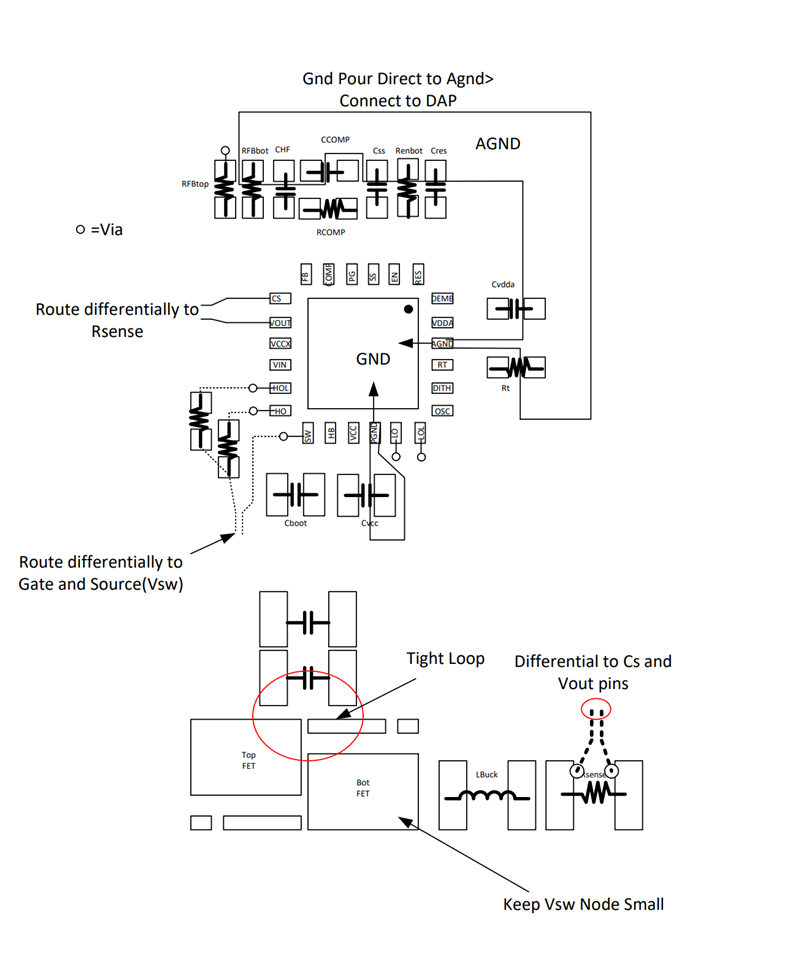

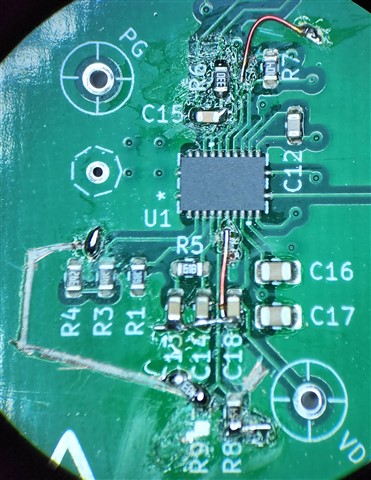

我正在开发基于 LM25148的电源转换器。 我的第一个设计不稳定、无法诊断问题、因此我备份了数据表中的2号典型设计。 我使用几乎相同的部分重新创建了设计、并从 LM25149EVM 紧密复制了布局。 请参阅下面的原理图:

我在参考设计中所做的唯一更改是将输出电压从5V 增加到12.8V。 我相应地增加了输出电容器的额定电压。 INA280应测量电感器电流以进行故障排除、但由于带宽和饱和限制、该器件可能是一个不好的选择。

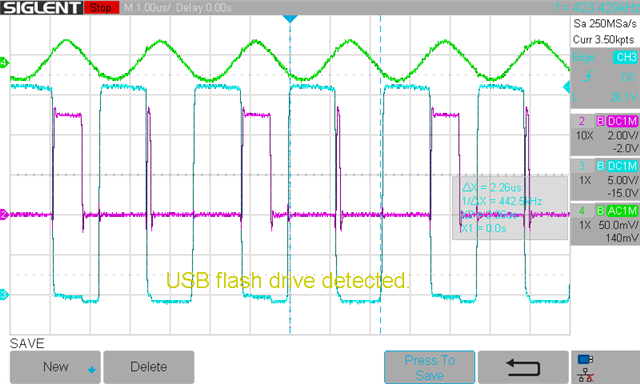

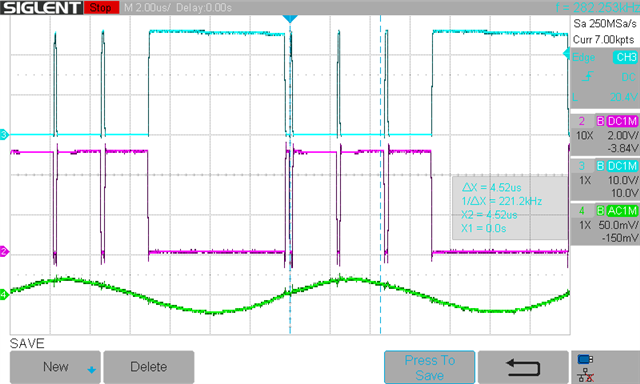

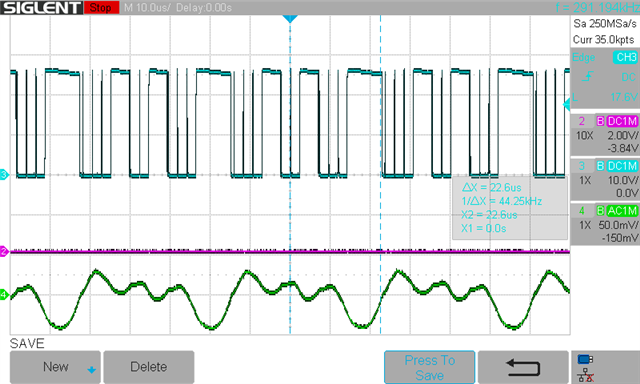

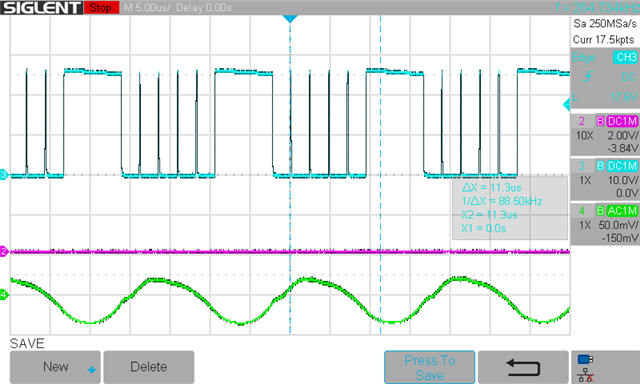

当负载超过~3.5A 时、我开始看到不一致的开关、如下面的示波器屏幕截图所示。 蓝色迹线表示 SW 节点、绿色迹线表示 Vout。

较长的脉冲后跟较短的脉冲(较小的脉冲宽度看起来就像最短导通时间)。

此行为取决于负载、并在负载增加和减少时表现出一定的迟滞。 更具体地说、不稳定将在一定的负载增加时开始、并且在负载降至问题开始时低于消耗时仍然存在。

我已使用 TI 设计计算器检查我的设计、我应该有超过78度的足够相位裕度和-18dB 的增益裕度。 我已采取以下步骤来解决我的问题:

1.为 ISNS+和 Vout 引脚添加滤波器、如 EVM 中所用

2.调整我的薪酬网络,以解决整体转换功能分析中的误差

3、购买并测试 TI 生产的 EVM、排除测试设备的问题

TI 的 EVM 似乎工作正常、排除了测试设备的故障、尽管总是存在边缘情况。 我已采取其他步骤对设备进行故障排除、例如各种筛选器和配置调整、但这些更改没有帮助、并且我没有很好地记录这些更改。

我感觉自己有点失落、因为我无法明白 EVM 为什么起作用、但我的设计却无法起作用。 如果需要、我可以提供布局文件和任何其他示波器截图。