关于规格 VIH>2.1V 是高电平, VIL<1.1V 是低 电平,为什么测试结果: VIH>1.6V 是高电 平, VIL<1.6V 是低电平,无电压窗口?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

关于规格 VIH>2.1V 是高电平, VIL<1.1V 是低 电平,为什么测试结果: VIH>1.6V 是高电 平, VIL<1.6V 是低电平,无电压窗口?

您好、Godwin:

很抱歉耽误你的时间。 TI 美国度过了一个假期、我们又回到了办公室。 我已经 用 英文制作了您的测试结果图表、以供搜索、并确保我了解您的问题。 如果我遗漏了任何内容、请更正我。

您能否分享您的 原理图以及 gpioC 和 gpioD 连接到的负载?

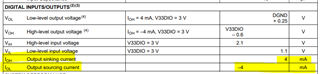

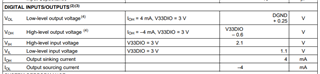

数据表指出最大输出拉电流和输入灌电流为4mA。 如果负载或灌电流超过4mA、则输出可能会低于 VOH、输入可能高于 VIL。 没有内部钳位来限制电压变化、因此这可能是您的行为的原因。

请 参阅以下 E2E 博文:

此致、

乔纳森·王

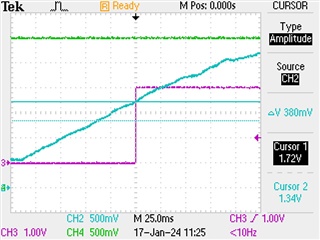

我们使用 EVM 板进行测试、型号为"UCD3138128OEVM-592 PWR592 REV。 E2."

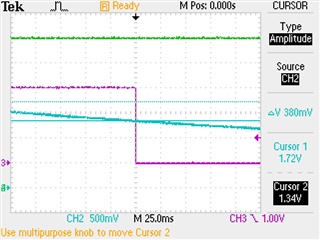

我们用示波器测试了3个信号:

CH2是输入 GPIOC 引脚。 (刻度为500mV)

CH3是输出 PWM2引脚。 刻度为500mV)

CH4是 V33D 引脚、 外部电源提供"3.0V"电压。 (比例为1V)

您好、Godwin:

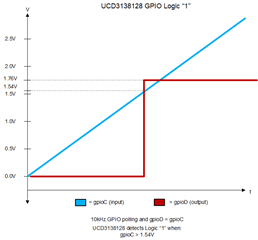

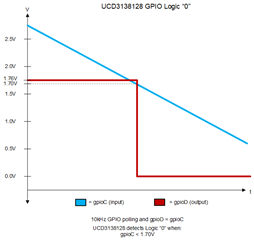

很抱歉让人感到困惑。 您显示的测试结果实际上在规格范围内。 数据表显示 VIH > 2.1V 且 VIL < 1.1V。 不过、这只是一个 得到保证 极周期。 为 1.1V - 2.1V 之间的行为未定义、可以是逻辑"1"或逻辑"0" 。

数据表仅保证 VIH > 2.1V 必须 返回逻辑"1"并使 VIL < 1.1V 必须 返回逻辑"0"。 因此、只要 VIH>1.1V 不 返回 逻辑"0"、 该行为就 在规格范围内。

在您的测试结果中,逻辑"1" 在>1.34V 之前不会出现。 这是可以的、因为1.34V 不小于1.1V。 任何低于1.1V 的电压 得到保证 设置为逻辑"0"。

反之亦然、 直至低于1.70V 时才会出现逻辑"0"。 这是可以的、因为1.70V 不大于2.1V。 任何 大于2.1V 的电压 得到保证 设置为逻辑"1"。 这是正常行为。

此致、

乔纳森·王