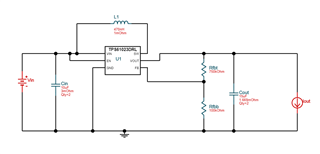

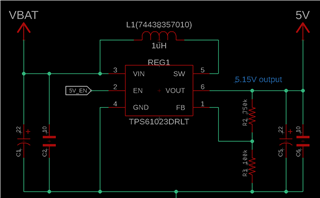

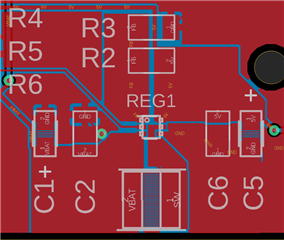

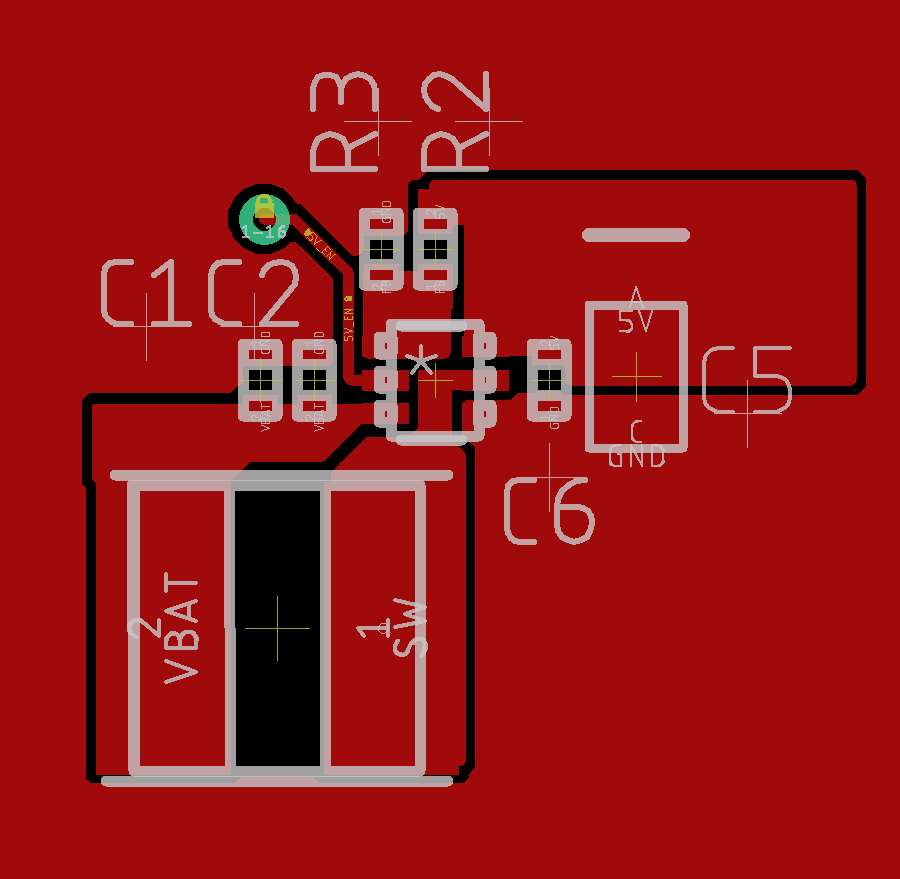

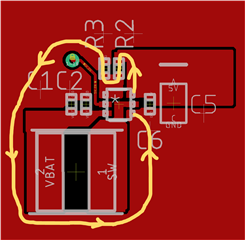

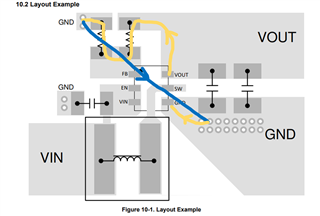

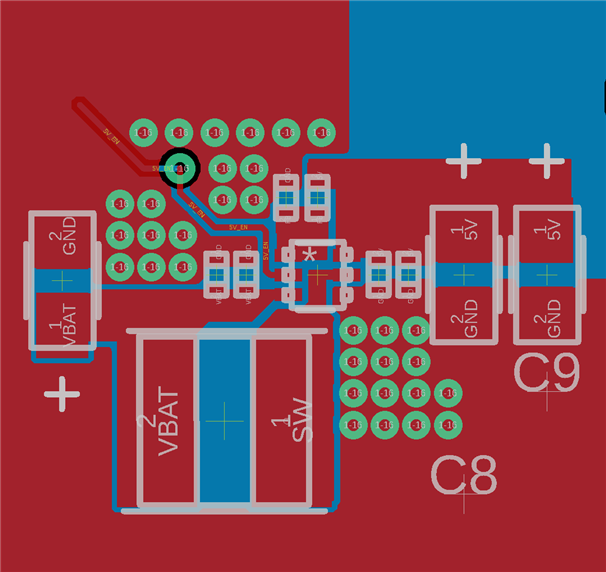

因此、我使用 webench 构建了该电路。 我已经连接了 SCH 和 PCB。 它只是一个2层 PCB、不会太多。

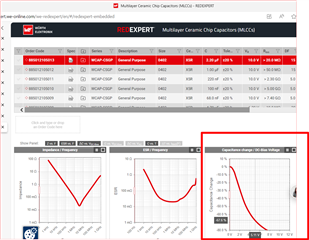

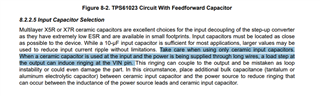

电路输出如广播所示为2.15V。 目前我连接了一个200mA 负载、一切都是 hunkey dorey。 当我把手指靠近芯片本身时、电压开始升高。 我的手指越近、输出电压就越高、直到我的手指触摸芯片并 炸薯条、造成从 VIN 到 GND 的完全短路。 我已经来过这里两次了! 我第三次添加了1pF 的前馈电容器(根据 webench 的建议)作为"还需做什么"解决方案。 我的逻辑是来自手指的杂散电容以某种方式影响 FB 引脚(因此输出电压不断增加)。 发生了同样的事情。 "到底怎么回事?" 我甚至可以尝试怎样开始进行故障排除?