此常见问题解答有助于解释为什么 DCAP+器件中存在抖动、当抖动是问题时、如何将其最小化。

COT 控制架构简介

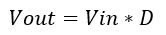

所有降压转换器控制方法的工作方式都是改变控制 FET 的占空比以调节输出电压。 除损耗外、降压转换器的输出电压平均如下(D=占空比):

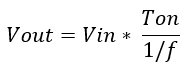

电压模式和峰值电流模式等更加传统的控制架构的工作原理是增加或减少导通时间、同时保持频率不变。 这可用于增加或降低输出电压、或稳定输出电压以响应负载瞬态。 重写上面的等式将 D 分解到它的各个分量中、我们得到下面的等式。 这清楚地说明了在理想情况下增加 Ton 如何成比例地增加输出电压。

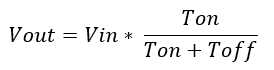

COT (恒定导通时间)控制架构(如 DCAP+)的工作原理是保持 Ton 不变并更改关断时间以实现所需的输出电压。 通过再次重写第一个等式可观察到效果:

由于导通时间不变、而关断时间不变、因此必须改变周期和频率才能改变占空比。 COT 控制架构的优势在于具有更好的瞬态响应和更轻松的调优、但代价是线性度更差且(通常)输出纹波更大。

这里需要注意的一点是、对瞬态的频率变化不是典型抖动、这是 COT (包括 DCAP+)器件的预期调节机制。

DCAP+中的抖动

DCAP+是适用于多相应用的 TI 专有控制架构。 从根本上说、这是一种恒定导通时间谷值电流模式控制方案、并添加了一些特性使其特别适用于多相电源。 点击以下链接可访问 DCAP+上有用的应用手册: https://www.ti.com/lit/an/slva867/slva867.pdf

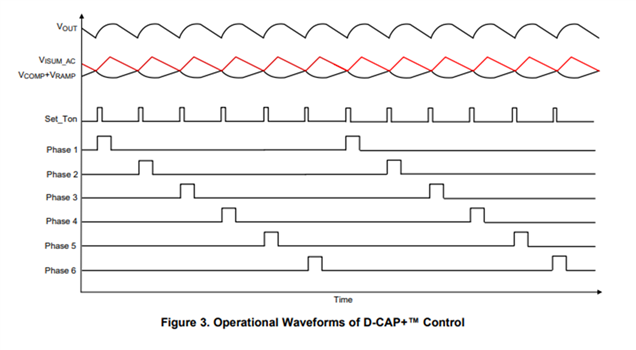

与抖动相关、最值得注意的观察结果是、当 Isum_ac (所有相位的瞬时电流之和)"触摸"Vcomp + Vramp 信号时、会触发一个新脉冲。 如下图所示:

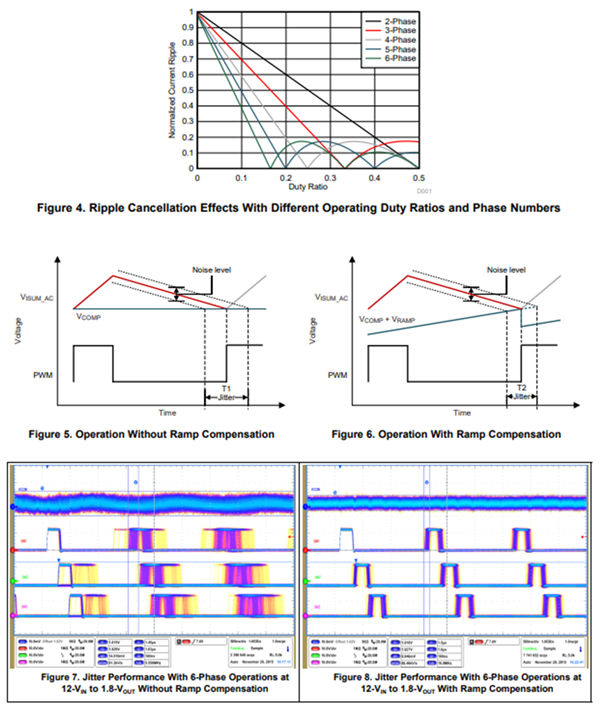

因此、ISUM 信号中的任何噪声都将略微延迟或略微提前开始新脉冲。 这是 DCAP+设计中常见的抖动形式之一。 这在高相位数设计中尤其明显、因为纹波消除可确保在开始的 ISUM 波形中有相对较小的纹波。 下面显示了有关该效果的更多详细信息(来自上述应用手册的第5页):

如图6和8所示、增大斜坡会降低 ISUM 噪声对每个脉冲的开始时间的影响、从而降低抖动。 对于高相位数设计、我们通常建议从440mV 斜坡开始、以更大限度地减少抖动。 较高的斜坡设置确实会降低瞬态性能、因此如果斜坡电压不能满足瞬态规格440mV、那么减小斜坡设置可能是最佳选择。 可以在 Fusion GUI 中的补偿部分中设置斜坡。

抖动和稳定性

DCAP+器件中的抖动不能降到零、也不必降至零。 抖动处于20-30%范围内并不少见、尤其是在低斜坡设置下。 只要瞬态响应看起来正常且没有双脉冲、从稳定性的角度来看、抖动通常不是问题。

高抖动确实会增加输出电压纹波、这可能是纹波敏感型轨的问题。 在这种情况下、增大斜坡可能是最佳做法。 如果将斜坡设置为最大值且仍然无法管理抖动、则表示存在不同的问题、例如噪声敏感性或环路不稳定。 如果是这种情况、则需要进行更有意义的分析。

谢谢。

特拉维斯·威廉姆斯

IPP MPP 应用工程师