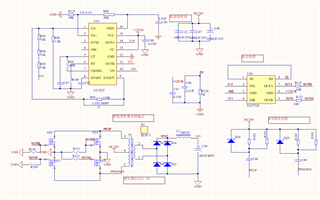

输入:直流12V (12V7AH 电池)

输出:直流110V

全桥场效应晶体管:IRF3205

变压器匝数比:NP:NS (7:80)

PWM 频率:15kHz

电感(L3):1mH

电容(C58):68uF/400V

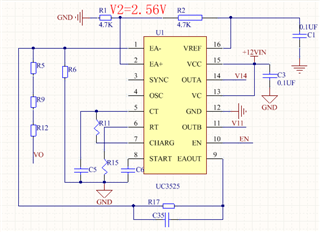

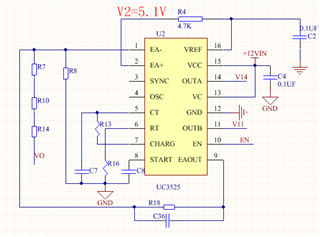

用于全桥整流的推挽式转换器的原理图如下

一些问题如下:

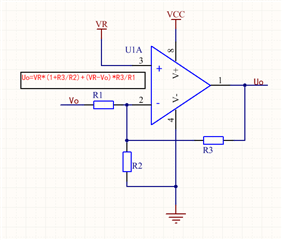

个人了解误差放大器有两个用途

1.运算放大器

所以 uo=uo=VR*(1+R3/R2)+(VR-Vo)*R3/R1

2.comparator

R3=100K,当推挽式转换器的输出电压由 R1和 R2电阻器分压并且大于 VR 时、误差放大器输出较低、而 UC3525的 PWM 占空比为零

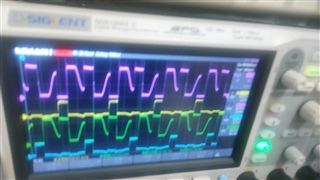

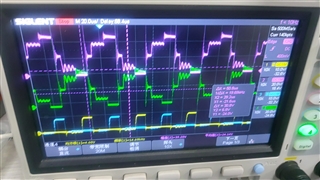

通过测试、我们发现第一类推挽式转换器的输出电压在空载时满足要求、但在带载时、Vds 波形不好、效率低

相反、根据第二种连接方法(比较器)、其负载 VDS 波形良好且高效

UC3525芯片的2个引脚(EA+)上的电压可被取为5.1V 基准电压的大约一半吗?

引脚2上的电压2.5V 和5.1V 对整个转换器有何影响?

英语能力有限、请原谅所有错误

我的最终目标是确定误差放大器是用作运算放大器还是用作比较器。 误差放大器的两个引脚上的不同基准电压对输出电压有何影响?

谢谢!