Other Parts Discussed in Thread: TPS745, TPS745-Q1

主题中讨论的其他器件:TPS745、

大家好、

您能帮助我确认当 TPS745上的 ENABLE 引脚为低电平时 PG 引脚的状态是什么吗? 应用使能之前它是高阻态、还是只要 Vin 有电压、它仍然是低电平? 当 ENABLE 引脚保持低电平时、它是否会根据 Vin 是否存在而变化?

谢谢。

本

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Juliette:

我认为当输出电压有效/良好时、PG 输出应该会变为高阻态、因为此时上拉电阻器会提供高电平信号来启用下游器件。 当它不好时、它应该拉低。

您的描述表明它会呈现高阻态并允许来自上拉电阻器的电压、就像即使器件未启用、输出电压也很好一样-正确吗?

我认为您针对 PG 行为展示的延迟时序与此处无关。

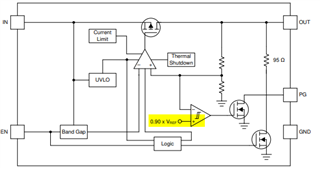

要以不同的方式说明问题、内部 PG 比较器的该 Vref 输入是否即使在 ENABLE 引脚被拉至低电平时也保持有效? 如果比较器的 Vref 输入仍然存在、则应根据 OUT 引脚上的电压不符合阈值、使 PG 引脚保持拉低状态、即使未通过 EN 引脚启用该器件也是如此:

谢谢。

本

您好、Ben、

你是对的、我说错了。

PG 的状态仅在 TPS745-Q1的工作电压高于器件的最低输入电压 且电源正常状态有效时才有效、无论输入电压低于 UVLO 阈值 减去 UVLO 迟滞时的输出电压状态如何。 当输入电压降至约0.8V 以下时、没有足够的栅极驱动电压来保持开漏电源正常状态器件开启并将电源正常状态输出拉至高电平。 将电源正常状态上拉电阻器连接到输出电压有助于将这种影响降至最低。

此致!

朱利耶特