请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMR51450 您好、团队成员:

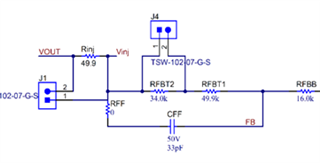

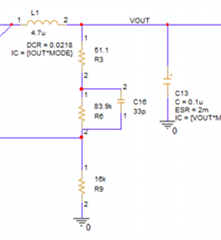

我 对如何设计 CFF 配置感到困惑。 所有设计在数据表、EVM 和 PSpice 参考原理图上都不同。

我应遵循哪种设计?

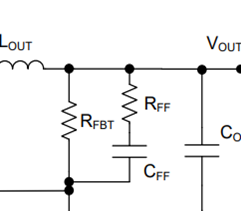

数据表

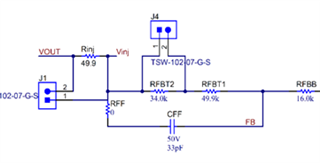

EVM

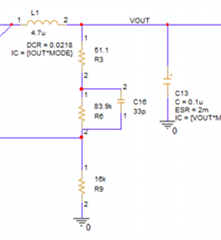

PSpice 参考原理图

此致、

桑原启

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、团队成员:

我 对如何设计 CFF 配置感到困惑。 所有设计在数据表、EVM 和 PSpice 参考原理图上都不同。

我应遵循哪种设计?

数据表

EVM

PSpice 参考原理图

此致、

桑原启

您好 Kuwahara-San、

数据表显示了 RFF 和 CFF。 Cff 是改善相位裕度和负载瞬态的主要贡献者。 Cff 可以 将电路输出端的噪声直接传导至 IC 的 FB 节点、因此可以将1-kΩ 电阻器 RFF 与 Cff 串联。

PSpice 中并未考虑耦合到 FB 的实际噪声、因此未包含该噪声。 EVM 上的设计有一个用于 RFF 的0 Ω 占位符、以防噪声耦合到 FB 并导致调节问题、终端用户可以放置任何 RFF 电阻器来帮助解决此问题。

请注意、RFF 不是必需的、而是最好使用组件、因此除非观察到噪声、否则不需要。

此致、

吉米