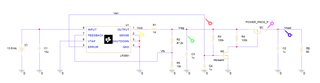

我尝试使用错误引脚通过 PMOS FET 切断负载。 我尽一切努力仿真、使 LP2951的输出(Vout)变为0V。 我预计它会在开/关之间振荡。 是我的设计和理解还是仿真模型导致了这种情况?

当我阅读数据表时、错误引脚对稳压器器件没有行为影响。

我同时尝试过 PSpice 和 LTSpice。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.