主题中讨论的其他器件:CSD17304Q3、 TPS51116

我在 DCAP 模式下使用 TPS51116作为1.35V 输出。 我将 RDS_ON 感测与高/低侧 TI CSD17304Q3 FET 配合使用。

我看到该器件在大约1.8A 输出时出现异常行为。 低于1.8A 时、该器件正常运行。 当我首次观察到此行为时、我增大了 RTRIP 电阻、认为器件处于 OC 限制状态、但即使在我增大电阻以增加 OC 限制之后、该器件仍在1.8A 再次关断。

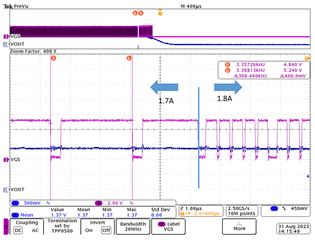

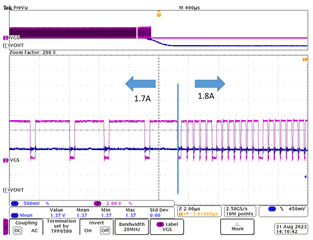

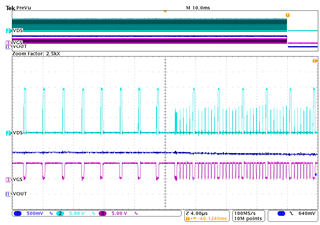

下面的示波器捕获(Vgs 低侧 FET 粉色、Vout 蓝色)显示了器件在低于1.8A 的400kHz 开关频率附近正常运行。 当负载电流超过1.8A 时、开关频率会增加至约2.2MHz。 我不认为该器件会进入2.2MHz 运行模式、正常频率设置为400kHz 左右。

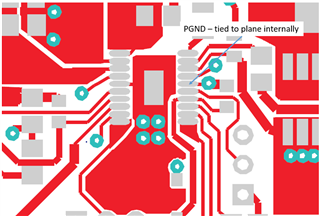

我还捕获了 LL 引脚(即青色开关节点)、因为在使用 RDS_ON 感测时该引脚兼作电流检测点。 开关节点似乎在振荡、这些节点随着 Vgs 增加频率而排列。 如果发生某种振荡、则开关节点上具有缓冲器 R 和 C、但我看不出输出电流越高、在负载电流越低时会产生振荡。

使用 RDS_ON 感测时、DCAP 模式是否需要感测电感器电流模式? 我想知道我是否应该将低侧 FET 更改为具有更高 RDS_ON 的部件、以便获得更大的信号来感测电感器电流。 我不确定输出为什么会以较低的电流和较少的信号工作、然后在 LL 引脚上有更多信号时开始在较高的电流下关闭、但这只是一个想法、如果输出变得不稳定。

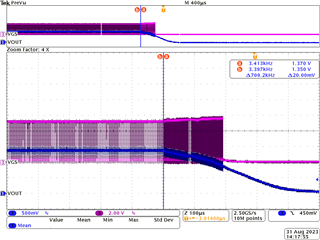

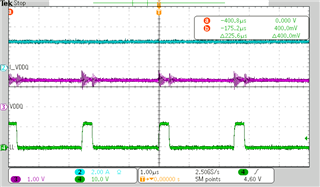

最后一个示波器捕获显示、当我将负载升至1.8A 时、1.35V 输出会缓慢下降至零。

有人以前见过这种行为吗?