请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LM5067 大家好、团队

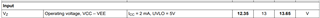

我想咨询一下 LM5067、客户当前的应用是这样的、VCC = 5V、VEE =-48V、这两个信号没有一起上电、在第一级 VCC = 5V、VEE = 0V; 第二级是 VCC = 5V、VEE =-48V 时、电流问题是当 VEE = 0V、LM5067的 Vout=5V = VCC、但客户后置芯片的最大电压不能超过0.3V、所以他们现在使用钳位二极管将 VCC 钳位到0.3V、所以我的问题是

、VEE 后、LM5067输出变为 VEE。 该芯片是否能够防止输出受到跟踪 VCC 的影响。

2.当 VCC = 5V、VEE = 0V 时、芯片处于 UVLO 阶段、为什么芯片的输出等于 VCC、导致它的具体路径是什么、可以发现 VOUT = VCC 的上升时间只有大约70ms。

3.芯片能否始终以 ULVO 状态工作?

4.钳位二极管是否可以长时间使用